# MJX440 for NB85E User's Manual

Rev. 1.12 2004/03/02

#### 変更履歴

| バージョン | 変更内容                                    | 変更日      |

|-------|-----------------------------------------|----------|

| 1.00  | ● 新規作成                                  | 02/03/18 |

| 1.01  | ● 付録「V850E/ME2内蔵命令 RAM の取り扱い」を追加        | 03/08/20 |

|       | <ul><li>■ コマンド「変更~I/O ポート」を追加</li></ul> |          |

| 1.02  | ● 誤字、脱字修正                               | 03/09/03 |

| 1.10  | ● コンフィグレーションファイルの設定画面の変更                | 04/02/09 |

| 1.11  | ● 誤字修正                                  | 04/02/27 |

| 1.12  | ● 誤字修正                                  | 04/03/02 |

#### ご注意

- 本マニュアルの一部または全部を無断で複製することはできません。

- 本製品を運用した結果の影響については、いかなる責任も負いません。

- 本製品の仕様および本マニュアルの内容は予告なく変更することがあります。

- Windows は、米国 Microsoft 社の登録商標です。

- MULTI は、米国 Green Hills Software 社の登録商標です。

@1999-2004 Lightwell Co., Ltd. All rights reserved.

Printed in Japan

住所: 〒167-0051 東京都杉並区荻窪 5-20-12

TEL: 03-3392-3331 FAX: 03-3393-3878

E-mail: ZAXSupport@lightwell.co.jp URL: http://www.lightwell.co.jp/ZAX/

2004年03月

この度は、MJX440 for NB85E(以下、本文中は MJX440)をご購入いただきまして、誠にありがとうございます。

本マニュアルの内容は、次のとおりです。

#### 第一章 概要

製品構成、MJX440の概略、各部の名称について記述しています。

#### 第二章 ホスト インターフェースの設定

ホストインターフェース(PCI/ PCMCIA カード)の取り付け方法と、 設定方法、デバイスドライバのインストール方法について記述しています。

#### 第三章 ハードウェアの接続

MJX440とホストの接続方法、MJX440とターゲット システムの接続方法について記述しています。

#### 第四章 ソフトウェアのインストール

MJX440を操作するソフトウェアのインストール方法について記述しています。

#### 第五章 MJX440 の環境設定

MJX440を使用する前に必要な、環境設定の方法について記述しています。

#### 第六章 ソフトウェアの起動と終了

MJX440を操作するソフトウェアの起動方法と終了方法について記述しています。

#### 第七章 MJX440 コマンド

MJX440コマンドの使い方について記述しています。

#### 第八章 MJXDEBW メニューコマンド

MJXDEBW メニューコマンドの使い方について記述しています。

#### 第九章 高速ダウンロード

高速ダウンロードを行なうための手順について記述しています。

#### 付録

仕様、ターゲットシステムの制限事項などの技術情報について記述しています。

### もくじ

| 第一章 概要              | 8  |

|---------------------|----|

| 1.1 製品構成            | 8  |

| 1.2 MJX440 の概略      | 11 |

| 1.3 各部の名称           | 15 |

| 第二章 ホスト インターフェースの設定 | 17 |

| 第三章 ハードウェアの接続       | 18 |

| 3.1 MJX440 とホストの接続  | 18 |

| 3.2 N-Wire ケーブルの接続  | 19 |

| 3.3 ROM プローブの接続     | 20 |

| 3.4 外部トリガ ケーブルの接続   | 27 |

| 3.5 電源の接続と電源投入手順    | 29 |

| 第四章 ソフトウェアのインストール   | 30 |

| 第五章 MJX440 の環境設定    | 37 |

| 第六章 ソフトウェアの起動と終了    | 39 |

| 第七章 MJXDEBW コマンド    | 43 |

| ABORT               | 46 |

| BATCH               | 47 |

| BP                  | 48 |

| CLEAR               | 50 |

| CONFIG              | 51 |

| DUMP                | 52 |

| EVENT               | 53 |

| EXAMINE             | 56 |

| FILL                | 57 |

| FLASH               | 58 |

| GO                  | 60 |

| HISTORY             | 61 |

| INIT                | 62 |

| JOURNAL             | 63 |

| LOAD                | 64 |

| MOVE                | 65 |

| OUTTRIG             | 66 |

| PIN                 | 67 |

| QUIT                | 68 |

| REGISTER            | 69 |

| SETLOAD             | 70 |

| SETSAVE                           | 71  |

|-----------------------------------|-----|

| STEP                              | 72  |

| TRACE                             | 73  |

| TRACE/A                           | 74  |

| TRACE/C                           | 75  |

| TRACE/M                           | 76  |

| TRACE/I                           | 78  |

| TRACE/R                           | 81  |

| UNASM                             | 82  |

| VERSION                           | 83  |

| WAIT                              | 84  |

| XPIN                              | 85  |

| 第八章 MJXDEBW メニューコマンド              | 86  |

| ファイル(F) ~ バッチ(B)                  | 87  |

| ファイル(F) ~ ジャーナル開始(S)              | 88  |

| ファイル(F) ~ ジャーナル停止(E)              | 88  |

| ファイル(F) ~ トレース結果(T)               | 89  |

| エミュレーション(E) ~ 実行(G)               | 90  |

| エミュレーション(E) ~ 再スタート(R)            | 90  |

| エミュレーション(E) ~ 中断(B)               | 91  |

| エミュレーション(E) ~ ステップ(S)             | 91  |

| エミュレーション(E) ~ N-ステップ(N)           | 92  |

| エミュレーション(E) ~ ダウンロード(L)           | 93  |

| エミュレーション(E) ~ 初期化(I)              | 94  |

| エミュレーション(E) ~ フラッシュメモリ(F) ~ 書込(W) | 95  |

| エミュレーション(E) ~ フラッシュメモリ(F) ~ 消去(E) | 96  |

| 表示(V) ~ メモリ(M)                    | 97  |

| 表示(V) ~ レジスタ(R)                   | 99  |

| 表示(V) ~ 逆アセンブル(D)                 | 100 |

| 表示(V) ~ トレース結果(T)                 | 101 |

| 表示(V) ~ コマンド応答クリア(C)              | 107 |

| 表示(V) ~ オプション(O) ~ フォント(F)        | 108 |

| 表示(V) ~ オプション(O) ~ 表示(V)          | 109 |

| 変更(M) ~ メモリ(M)                    | 110 |

| 変更(M) ~ I/O ポート(P)                | 111 |

| 変更(M) ~ レジスタ(R)                   | 112 |

| 変更(M) ~ アセンブラ(A)                  | 113 |

| 変更(M) ~ フィル(F)                     | 114 |

|------------------------------------|-----|

| 変更(M) ~ 移動(M)                      | 115 |

| 設定(S) ~ ブレークポイント(B)                | 116 |

| 設定(S) ~ トレース(T)                    | 118 |

| 設定(S) ~ イベント(E)                    | 122 |

| 設定(S) ~ 設定の読出(L)                   | 125 |

| 設定(S) ~ 設定の保存(S)                   | 126 |

| 設定(S) ~ コンフィグレーション(C) ~ 設定(S)      | 127 |

| 設定(S) ~ コンフィグレーション(C) ~ 表示(V)      | 129 |

| 設定(S) ~ コンフィグレーション ~ 上書き保存(E)      | 130 |

| 設定(S) ~ コンフィグレーション ~ 名前を付けて保存(A)   | 131 |

| ヘルプ(H) ~ トピックの検索(H)                | 132 |

| ヘルプ(H) ~ MJXDEBW のバージョン情報(A)       | 133 |

| 第九章 高速ダウンロード                       | 134 |

| 付録 A 仕様                            | 135 |

| 付録 B ターゲット システムの制限事項               | 136 |

| 付録 C NーWireコネクタ                    | 137 |

| 付録 D ROM プローブ                      | 139 |

| 付録 E 対応 ROMピンアサイン                  | 145 |

| 付録 F LED                           | 149 |

| 付録 G レジスタ名一覧                       | 150 |

| 付録 H MJX バイナリ ファイル                 | 151 |

| 付録 I ターゲット システムへのプロービング            | 152 |

| 付録 J フラッシュ メモリ デバイス情報定義 ファイル レイアウト | 158 |

| 付録 Κ 対応フラッシュ メモリー覧                 | 162 |

| 付録 L V850/ME2 内蔵命令 RAM の取り扱い       | 176 |

| 検索項目                               | 177 |

### 第一章 概要

製品構成、MJX440の概略、各部の名称について記述しています。

### 1.1 製品構成

出荷時の MJX440 for NB85E パッケージの中には、次のものが含まれています。 万一、 欠品がございましたら、 弊社までご連絡ください。

□ MJX440 for NB85E 本体

□ AC アダプタ

□ AC コード

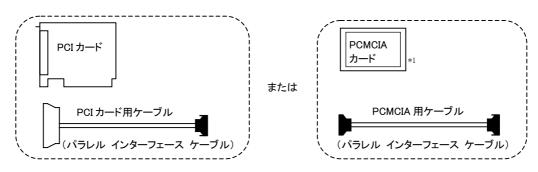

□ ホスト インターフェース

□ N-Wire ケーブル

<sup>\*1</sup> カードの正しい名称は「PC カード」です。

PCMCIA(Personal Computer Memory Card International Association)は PC カードの標準化団体名ですが、このマニュアルでは PC カードを全て「PCMCIA カード」と表記しています。

| $\square$ ROM プローブ* $^{1}$ 2 本(J-101A、J-102A、J-103A または J-104 | A 各2本)                                         |

|---------------------------------------------------------------|------------------------------------------------|

|                                                               |                                                |

| □ ROM プローブ ケーブル2 *1本                                          |                                                |

|                                                               |                                                |

| □ 外部トリガ ケーブル 1 種類                                             |                                                |

|                                                               |                                                |

| ロマニュアル2冊                                                      |                                                |

| Manual MJX440 for NB85E User's Manual                         | MJX440<br>HostInterface<br>Installation Manual |

|                                                               |                                                |

| 保証書                                                           |                                                |

| □ ユーザー登録カード <b>ューザ登録カード</b> 【重要】ユーザー登録カードは、必要事までご返送ください。      | 事項をご記入の上、弊社                                    |

| □ CD-ROM                                                      |                                                |

|                                                               |                                                |

<sup>\*1</sup> ROM の種類によって、出荷時に含まれている ROM プローブが異なります。 詳しくは、「表 1-1 出荷時の ROM プローブ」を参照してください。

ただしエミュレーションメモリなしモデルには ROM プローブおよび ROM プローブケーブルは添付されません。

出荷時の ROM プローブは、次のとおりです。 ROM の種類によって異なります。

|                 | ROM プローブ*1 |                               |  |

|-----------------|------------|-------------------------------|--|

| ROM の種類         | ROM プローブ基板 | ROM プラグ*2                     |  |

| 27010(8bit)     | J-101A×2本  | $32 \text{pin} \times 4^{*3}$ |  |

| 27020(8bit)     |            |                               |  |

| 27040(8bit)     |            |                               |  |

| 27080(8bit)     |            |                               |  |

| 271000(8bit)    |            |                               |  |

| 27C4000(16bit)  | J-102A×2本  | 40pin×2                       |  |

| 27C8000(16bit)  | J-102A×2本  | 42pin×2                       |  |

| 27C16000(16bit) |            |                               |  |

| 271024(16bit)   | J-103A×2本  | 40pin×2                       |  |

| 272048(16bit)   |            |                               |  |

| 274096(16bit)   |            |                               |  |

| 27C4000(8bit)   | J-104A×2本  | $40$ pin $\times 4^{*3}$      |  |

| 27C8000(8bit)   | J-104A×2本  | $42 \text{pin} \times 4^{*3}$ |  |

| 27C16000(8bit)  |            |                               |  |

表 1-1 出荷時の ROM プローブ

<sup>\*1</sup> ROM プローブの詳細な図は「1.3 各部の名称」、「ROM プローブ」および「付録 D ROM プローブ」を参照してください。

$<sup>^{*2}</sup>$  ROM のピン数と接続可能な最大 ROM 個数です。実際の接続数はターゲットシステムにより異なります。

<sup>\*3</sup> ROM プローブ基板 J -101A、J -104A は ROM プラグが2本あるため、同時に2つに接続出来ます。

### 1.2 MJX440 の概略

MJX440 for NB85E は、N-Wireコネクタを備えた NB85Eコアを搭載した ASIC プロセッサのターゲット システムをデバッグ するための、開発支援装置です。

#### MJX440 のおもな特長

- ターゲット システムのN-Wire コネクタを使用するため、接続が簡単です。

- 高速な CPU でも安定して動作します。

- 任意で、ROM インサーキット接続ができます。ROM 上のプログラムもデバッグできます。

- 高級言語デバッガMULTIが使用できます。

- MJXDEBWデバッガ上で<u>MJXDEBWコマンド</u>が使用できます。MJX440が持つ機能をフルに使用できます。

- リアルタイムトレース機能があります。

- ハードウエアブレークポイント機能があります。

- プログラムのダウンロードが高速です。

N-Wire 接続時 480K バイト/秒 \*¹ (JTAG クロック 25MHzの場合)

ROM インサーキット接続時 4M バイト/秒

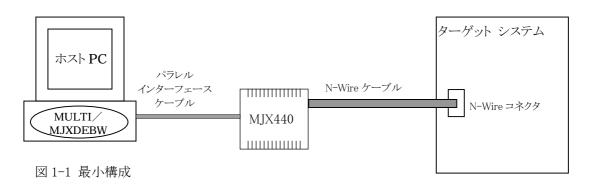

#### 最小構成

<sup>\*1</sup> ダウンロードの速さは、JTAGクロックを高く設定する程、高速になります。

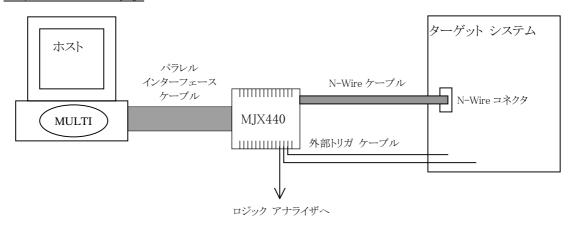

MJX440 は図 1-1 の最小構成で動作します。最小構成で使用した場合は、ターゲット システムの RAM 上のプログラムをデバッグすることができます。 プログラムは N-Wire ケーブルをとおして、ターゲット システム上の RAM ヘダウンロードされます。

最小構成の場合、ROM 上のプログラムを実行することはできますが、ROM 領域にプログラムをダウンロードしたり、ソフトウェア ブレークポイントを設定することができません。ROM 上のプログラムをデバッグする場合は、さらに ROM インサーキット接続する必要があります。

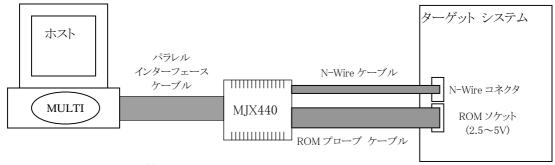

#### ROM インサーキット接続

図 1-2 ROM インサーキット接続

図 1-2 のように、ROM インサーキット接続した場合は、ROM 上のプログラムもデバッグできるようになります。ROM 上のプログラムは、ターゲット システムの RAM ではなく、MJX440 内のエミュレーション メモリ ヘダウンロードされます。

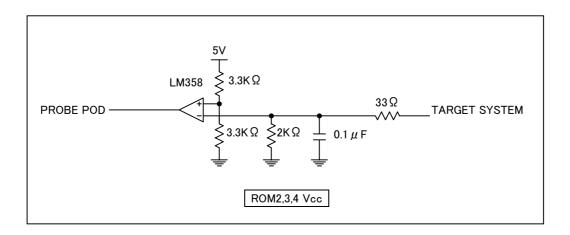

また、ROMの電圧は、2.5~5Vの範囲内で自動認識されます。

#### 外部トリガ ケーブル接続

図 1-3 外部トリガ ケーブル接続

図 1-3 のように、外部トリガケーブルを接続し、次の機能を実現させることができます。

- MJX440 コマンドから操作できる汎用信号をターゲット システムに出力する。(出力)

- ターゲットシステムの信号の状態を、MJX440上のLEDに表示させる。(入力)

- トレース トリガを、ロジック アナライザのトリガ信号として使用する。(出力)

- ターゲット システムの信号の状態を、リアルタイム トレース情報として記録する。(入力)

- 外部入力信号でターゲット プログラムをブレークする。(入力)

#### MJX440 を使用する前の準備作業

MJX440 を使用する前には、次の準備作業が必要です。第二章から第五章までを参照して行なってください。「ハードウエアの接続」以外は、購入時に一度だけ行なえばよい作業です。

- ホスト インターフェースの設定

- ハードウェアの接続

- ソフトウェアのインストール

- MJX440 の環境設定

準備作業が終了したら、第六章を参照して、MJX440 を操作するソフトウェア(MULTIまたはMJXDEBW)を起動してください。ソフトウェアが正常に起動できれば、準備作業は終了です。ソフトウェアが正常に起動できなかった場合は、準備作業に誤りがないか、確認してください。

コンパイラや MULTI の使い方については、それぞれのマニュアルとリリース ノートを参照してください。 また、MJX440独自の機能を使用するためのMJX440コマンドは、<u>第七章</u>および<u>第八章</u>を参照してください。

高速ダウンロードについては、第九章を参照してください。

#### MULTI について

MULTI はいろいろな環境で実行することができる高級言語デバッガです。サーバープログラム MJXSERV を呼び出すことによって、MJX440 の環境で実行させることができるようになります。

#### MJXDEBW について

MJXDEBW は MJX440 コマンドのみをサポートする簡易デバッガです。 高級言語デバッグをしない場合 や、バッチ処理機能を使って、ターゲット システムの検査をする場合などに使用することができます。

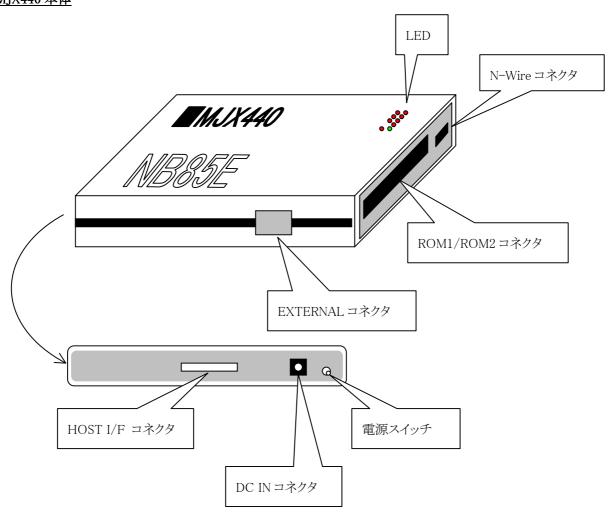

### 1.3 各部の名称

#### MJX440 本体

電源スイッチ ON で電源投入、OFF で電源切断します。

DC IN コネクタ AC アダプタを接続します。

HOST I/F コネクタ ホスト インターフェース ケーブルを接続します。

N-Wire コネクタ N-Wire ケーブルを接続します。

ROM1/ROM2コネクタ ROMプローブ ケーブルを接続します。上部がROM1、下部が

ROM2コネクタです。

EXTERNAL コネクタ 外部トリガ ケーブルを接続します。

LED 電源やコネクタの接続状態を表示します。

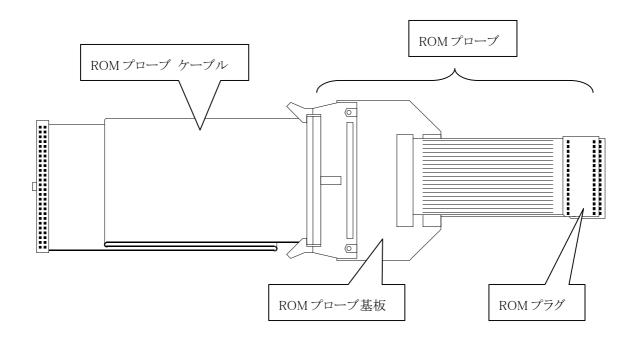

#### ROM プローブ

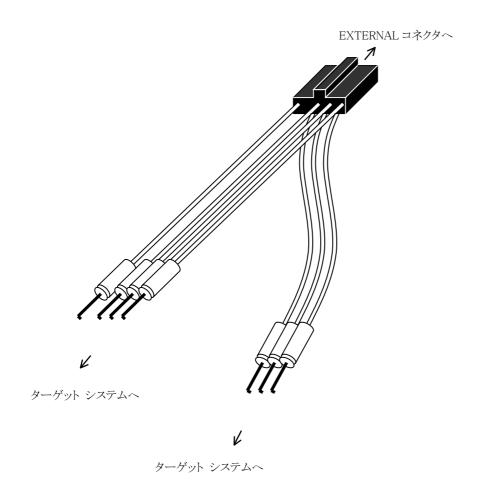

ROM プローブ ケーブル MJX440 と ROM プローブを接続するケーブル

ROM プローブ ターゲット システムの ROM へ接続するプローブ全体の総称

ROM プローブ基板 ROM プローブの基板部分(<u>ジャンパ設定</u>があります) ROM プラグ ターゲット システムの ROM ソケットへ接続する部分

## 第二章 ホスト インターフェースの設定

ホスト インターフェース(PCIカード、またはPCMCIAカード)の取り付け方法と、そのデバイス ドライバのインストール方法については、次の別冊マニュアルを参照してください。

### 第三章 ハードウェアの接続

MJX440 とホストの接続方法、MJX440 とターゲット システムの接続方法について記述しています。

【重要】MJX440と他の機器との接続は、必ず機器の電源を切ってから行なってください。

### 3.1 MJX440 とホストの接続

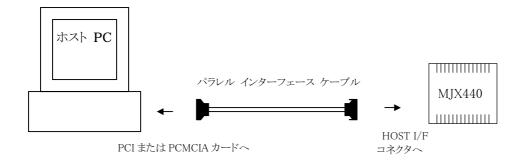

ホストに取り付けた PCI カード、または PCMCIA カードと、MJX440 のHOST I/F コネクタを、パラレル インターフェース ケーブルで接続してください。

図 3-1 MJX440 とホストの接続 /パラレル接続

【注意】PCMCIA 用ケーブルのカードとの接続コネクタの厚みにより、以下の制限事項があります。

- ◆ PCMCIAカード スロットが2つある場合でも、カードを1枚しか使用できない場合があります。 また、下のスロットにしかカードを差せない場合があります。

- ◆ カード 2 枚を無理に差し込むと、PCMCIA カード スロット、および PCMCIA カードのコネクタ 部が壊れる場合があります。

- ◆ PCMCIA カード スロットが 1 つだけの機種では、使用できない場合があります。

### 3.2 N-Wire ケーブルの接続

#### N-Wire プローブ

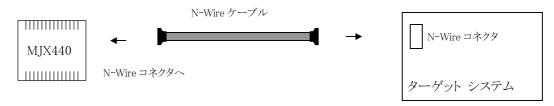

MJX440 のN-Wire コネクタと、ターゲット システム上の N-Wire コネクタを、N-Wire ケーブルで接続してください。

図 3-2 N-Wire ケーブルの接続

【注意】コネクタには向きがあります。コネクタの△マーク同士を合わせるように、接続してください。

### 3.3 ROM プローブの接続

ROM プローブの接続は、ROM インサーキット接続をする場合のみ必要な作業です。

はじめに、ROM の種類に合わせて、ROM プローブ<u>基板のジャンパを設定</u>してください。詳しい設定方法は、「付録 D ROM プローブ」を参照してください。

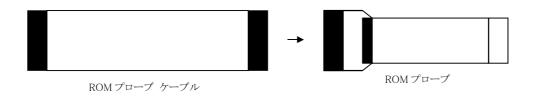

つぎに、添付されている ROM プローブを、ROM プローブ ケーブルに接続してください。

図 3-3 ROM プローブと ROM プローブ ケーブルの接続 1

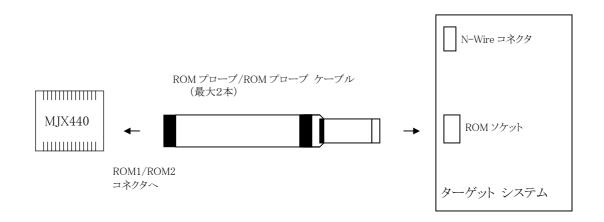

つぎに、ROM プローブをターゲット システムの ROM ソケットへ接続し、もう一方の ROM プローブ ケーブルを MJX440 の ROM1/ROM2 コネクタへ接続します。\*1

図 3-4 ROM プローブと ROM プローブ ケーブルの接続 2

<sup>\*1</sup> 必要な ROM プローブ本数は使用する ROM のタイプと個数により異なります。

#### 第三章 ハードウエアの接続

ROM プローブの接続方法は、ターゲットシステムの次の項目によって異なります。

- ROM1個あたりのデータ バス幅

- ROMの個数

- ROM 全体でのアクセス バス幅

図 3-5-1~3-5-9 の中から、ターゲット システムと一致する接続図をひとつ選び、図にしたがって ROM プローブと ROM プローブ ケーブルを接続してください。

【注意】MJX440 およびターゲット システムの電源を切ってから行なってください。

【注意】ROM プローブを逆差ししないでください。

【注意】 ROM プローブ J-101A と J-104A に接続できる二つの ROM プラグは、ROM プローブ基板上のシルク印刷文字(JROM1 または JROM2)で区別してください。

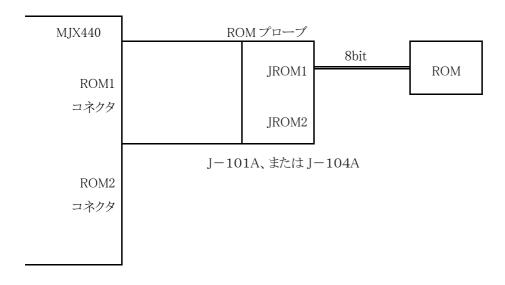

バス幅 8 ビット ROM 1 個、ROM アクセス バス幅 8 ビットの場合 (点灯 LED: ROM1)

図 3-5-1 ROM プローブの接続 1

バス幅 8 ビット ROM 2 個、ROM アクセス バス幅 8 ビットの場合 (点灯 LED: ROM1)

図 3-5-2 ROM プローブの接続 2

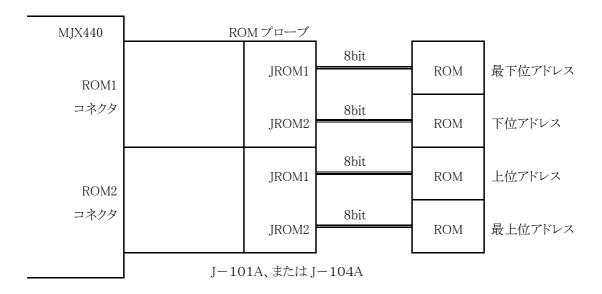

バス幅 8 ビット ROM 4 個、ROM アクセス バス幅 8 ビットの場合 (点灯 LED: ROM1、ROM2)

図 3-5-3 ROM プローブの接続 3

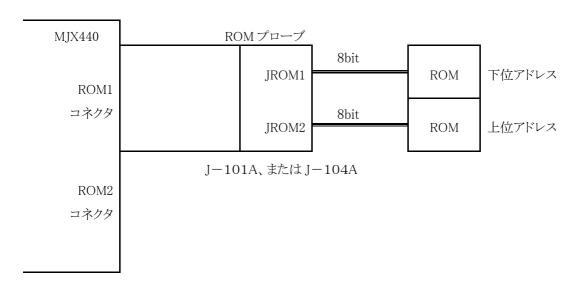

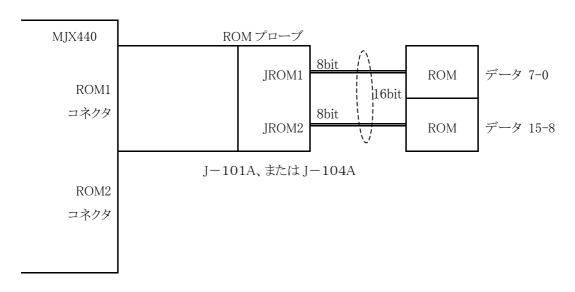

バス幅 8 ビット ROM 2 個、ROM アクセス バス幅 16 ビットの場合 (点灯 LED: ROM1)

図 3-5-4 ROM プローブの接続 4

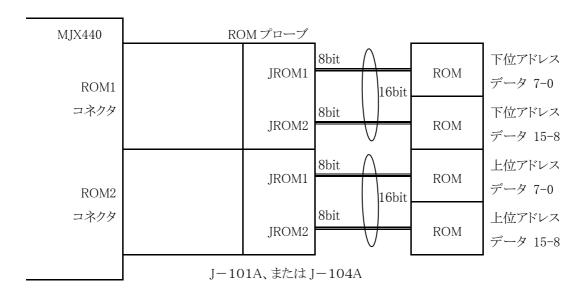

バス幅 8 ビット ROM 4 個、ROM アクセス バス幅 16 ビットの場合 (点灯 LED: ROM1、ROM2)

図 3-5-5 ROM プローブの接続 5

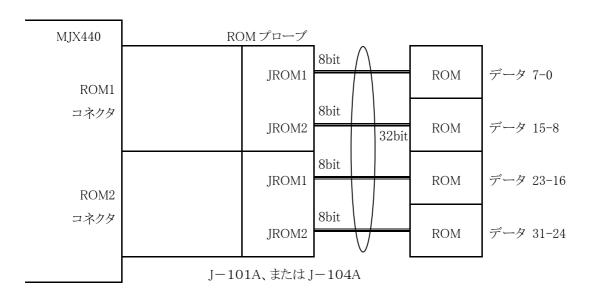

バス幅 8 ビット ROM 4 個、ROM アクセス バス幅 32 ビットの場合 (点灯 LED: ROM1、ROM2)

図 3-5-6 ROM プローブの接続 6

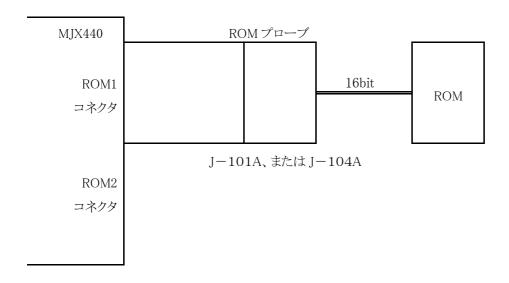

バス幅 16 ビット ROM 1 個、ROM アクセス バス幅 16 ビットの場合 (点灯 LED: ROM1)

図 3-5-7 ROM プローブの接続 7

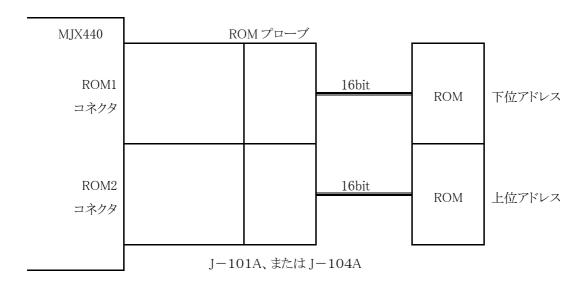

バス幅 16 ビット ROM 2 個、ROM アクセス バス幅 16 ビットの場合 (点灯 LED: ROM1、ROM2)

図 3-5-8 ROM プローブの接続 8

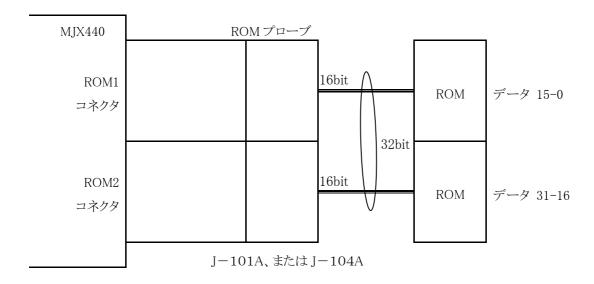

バス幅 16 ビット ROM 2 個、ROM アクセス バス幅 32 ビットの場合 (点灯 LED: ROM1、ROM2)

図 3-5-9 ROM プローブの接続 9

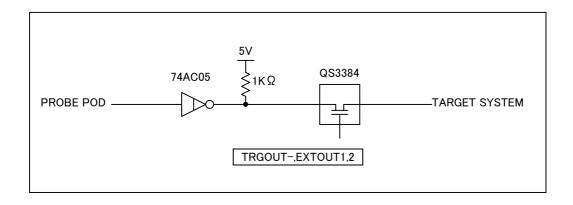

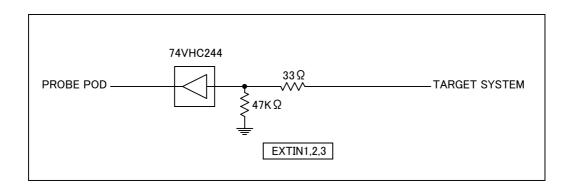

# 3.4 外部トリガ ケーブルの接続

ターゲット システムの信号の状態をLED に表示させたり、MJX440 が出力するトレース トリガ信号をロジック アナライザの入力として使用する場合は、外部トリガ ケーブルを使用します。これらの機能を使用しない場合は、外部トリガ ケーブルを接続する必要はありません。

図 3-5 外部トリガ ケーブルの接続

#### 第三章 ハードウエアの接続

外部トリガケーブルの信号の詳細は、次のとおりです。信号は、クリップとケーブルの色で区別します。

| 信号名     | 色      | 入出力           | 機能                               |

|---------|--------|---------------|----------------------------------|

| EXTIN1  | クリップ 黄 | TTL 入力        | 接続した信号が HIGH レベルの場合、対応する         |

|         | ケーブル 茶 |               | LED が点灯します。*1 また、EXTIN1 と EXTIN2 |

| EXTIN2  | クリップ 黄 | TTL 入力        | については、リアルタイム トレースにも、信号の          |

|         | ケーブル 赤 |               | 状態が記録されます。                       |

| EXTIN3  | クリップ 黄 | TTL 入力        | EXTIN3はターゲット プログラムのブレーク信号        |

|         | ケーブル 橙 |               | として使用できます。                       |

| EXTOUT1 | クリップ 赤 | 3.3V O.D.出力*2 | MJX440 コマンドの XPIN コマンドで、LOW また   |

|         | ケーブル 茶 |               | は HIGH レベルを出力します。                |

| EXTOUT2 | クリップ 赤 | 3.3V O.D.出力   |                                  |

|         | ケーブル 赤 |               |                                  |

| TRGOUT- | クリップ 緑 | 3.3V O.D.出力   | トレース トリガ以降 LOW レベルを出力します。        |

|         | ケーブル 緑 |               | ロジック アナライザのトリガ入力として使用でき          |

|         |        |               | ます。                              |

| GND     | クリップ 黒 |               | ターゲット システムの GND に接続します。          |

|         | ケーブル 黒 |               |                                  |

<sup>\*1</sup> MJX440 本体上の信号名は、EXTIN3→EXI 3 のように省略して表記されています。

<sup>\*2</sup> O.D.は、オープン ドレインの略です。

### 3.5 電源の接続と電源投入手順

すべてのケーブルの接続が終了したら、AC アダプタと AC コードを接続してください。このとき、MJX440 の電源スイッチが OFF の状態になっていることを確認してください。

機器の電源投入は、次の手順で行なってください。

- 1. ホスト PC

- 2. MJX440

- 3. ターゲット システム

機器の電源切断は、次の手順で行なってください。

- 1. ターゲット システム

- 2. MJX440

- 3. ホスト PC

【重要】電源投入および切断の手順を間違えると、機器が破壊される場合があります。

【重要】電源投入時には、機器の接続および着脱をしないでください。

# 第四章 ソフトウェアのインストール

MJX440を操作するソフトウェアのインストール方法について記述しています。

インストールは、以下の手順にしたがって行ってください。

- 1. Green Hills Software 社の統合開発環境 MULTI をインストールします。

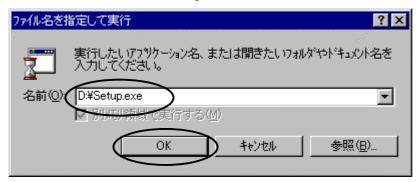

- 2. CD-ROMドライブに「MJX for NB85E Tools Disk」の CD-ROM をセットします。

「スタート」、「ファイル名を指定して実行(R)...」の順に選択し、「ファイル名を指定して実行」ダイアログを表示します。

3. 「**名前(O)**」にセットアップ プログラム Setup.exe を指定し、「**OK**」をクリックします。(CD-ROMドライブ が Dドライブの場合、「**D:¥Setup.exe**」)

4. セットアップ プログラムが起動します。

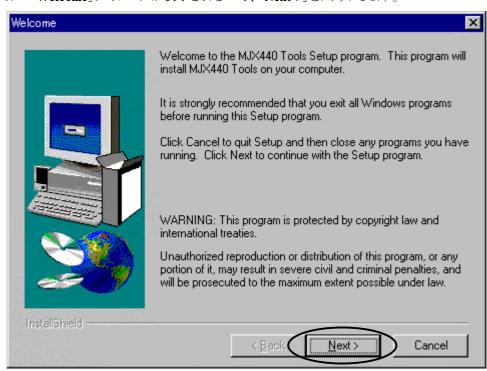

5. 「Welcome」ダイアログが表示されるので、「Next >」をクリックします。

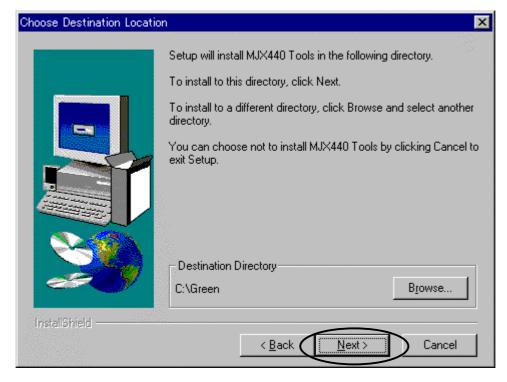

6. 「Choose Destination Location」ダイアログが表示されるので、「Browse...」ボタンをクリックしてインストール先を指定します。 <u>先にインストールした MULTIと同じディレクトリを、インストール先に指定してください。</u>(デフォルトは「C:¥Green」です)

「Next >」をクリックします。

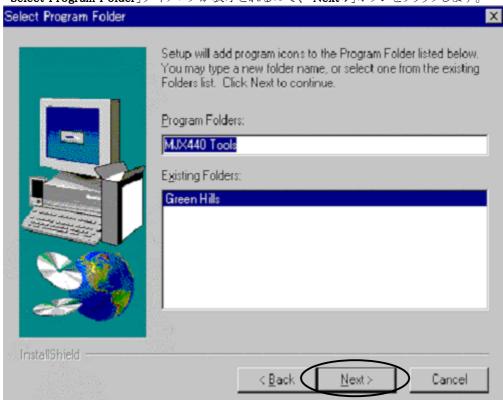

「Select Program Folder」ダイアログが表示されるので、「Next >」ボタンをクリックします。

- 7. インストールが開始します。

- 8. インストールが終了すると、作成されたプログラムフォルダが表示されます。

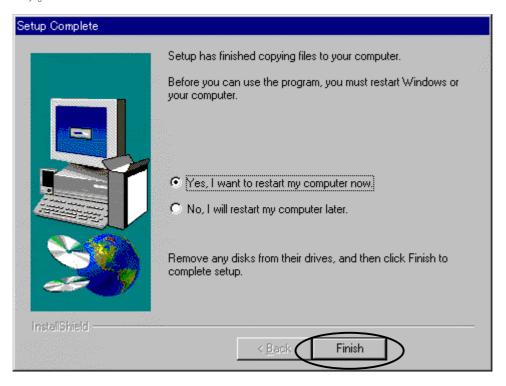

9. 「Setup Complete」ダイアログが表示されるので、「Finish」ボタンをクリックし、システムを再起動します。

【重要】インストーラはシステムディレクトリ\*1にライブラリMSVCRT.DLLをインストールします。 古いライブラリはMSVCRTxx. DLL(xxはバージョン番号)のようにリネームされます。

<sup>\*1</sup> システムディレクトリのデフォルトは、Windows9xの場合はC: \Windows\YSystem、WindowsNT4. 0およびWindows2000では、C:\Winnt\YSystem32です。

#### 第四章 ソフトウエアのインストール

インストールされるファイルは次のとおりです。

MJXDEBW.EXE 簡易デバッガ プログラム MJXDEBW

MJXCFG.EXE コンフィグ支援ツール MJXCFG (コンフィグレーション ファイル作成用)

MJXSERV.EXE MJX 用 MULTI サーバー プログラム MJXSERV

MJXCVT.EXE MJX バイナリ ファイル変換プログラム MJXCVT

WNTIX.EXE インストール用プログラム (使用しない)

MJX4020.INI MJXDEBW 用コンフィグレーション ファイルのサンプル (CW4020)

MJX4102.INI MJXDEBW 用コンフィグレーション ファイルのサンプル (TR4102)

MJXARM.INI MJXDEBW 用コンフィグレーション ファイルのサンプル (ARM9)

MJXNB85E.INI MJXDEBW 用コンフィグレーション ファイルのサンプル (NB85E)

MJXV831.INI MJXDEBW 用コンフィグレーション ファイルのサンプル (V831)

MJXV832.INI MJXDEBW 用コンフィグレーション ファイルのサンプル (V832)

Mjx4kc.INI MJXDEBW 用コンフィグレーション ファイルのサンプル (MIPS4kc)

MjxVR55.INI MJXDEBW 用コンフィグレーション ファイルのサンプル (VR5500)

MJXDBAPI.DLL MJXSERV-MJXDEBW 通信ライブラリ

MJXASM.DLL アセンブラ/逆アセンブラ ライブラリ

MJXARM.DLL ARM ライブラリ

MJXEJTAG.DLL TR4102/CW4020 ライブラリ

MJXNB85E.DLL NB85E ライブラリ

MJXV831.DLL V831 ライブラリ

MJXV832.DLL V832 ライブラリ

MJ2Ej2R6. DLL EJTAG2.5/2.6 ライブラリ

Mj2VR55.DLL V5500 ライブラリ

MSVCP60.DLL Microsoft Visual C++ ランタイム ライブラリ

MSVCRT.DLL Microsoft Visual C++ ランタイム ライブラリ

CfgResource.DLL コンフィグリソース ライブラリ

MjxARMJ.PDF ARM 和文へルプのファイル

MjxEJtgJ.PDF CW4020/TR4102 和文へルプのファイル

MjxEJtgE.PDF CW4020/TR4102 英文へルプのファイル

MjxNB85J.PDF NB85E 和文へルプのファイル

MjxCfgJ.PDF コンフィグレーションヘルプ画面のファイル

MjxifJ.PDF ホストインターフェース 和文ヘルプのファイル

MjxifE.PDF ホストインターフェース 英文ヘルプのファイル

MjxV83XJ.PDF V831/V832 和文へルプのファイル

MjxV83XE.PDF V831/V832 英文ヘルプのファイル

MIX440.ICO MIX440 アイコン ファイル

#### 第四章 ソフトウエアのインストール

MjxCARMJ.PDF MJX330 for ARM 和文へルプのファイル

Mj2CARMJ.PDF MJX330 for ARM (汎用品) 和文ヘルプのファイル Mj2CEj26J.PDF MJX330 for EJTAG2.5/2.6 和文ヘルプのファイル

MjxCNB85J.PDF MJX330 for NB85E 和文ヘルプのファイル Mj2CVR5J.PDF MJX330 for VR5500 和文ヘルプのファイル プロセスとハードウェアの構成は次のとおりです。

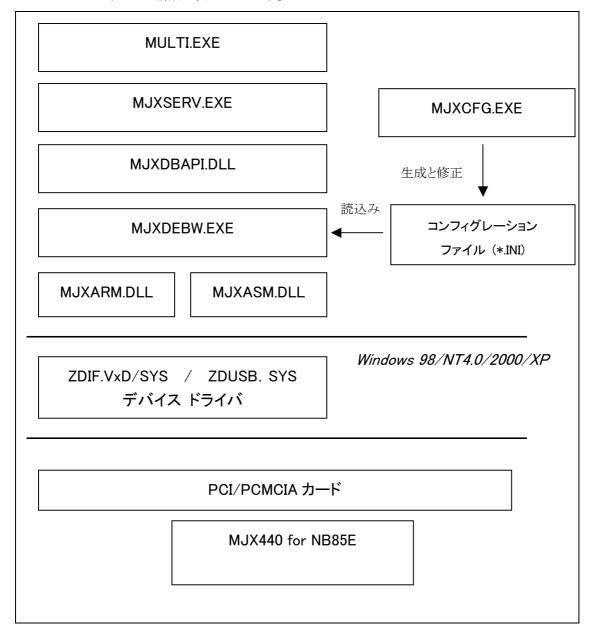

図 4-1 プロセスとハードウェアの構成/Windows

- MULTI.EXE は MJXSERV.EXE を子プロセスとして呼び出します。

- MJXSERV.EXE は MJXDBAPI.DLL を経由して MJXDEBW.EXE を子プロセスとして呼び出します。

- MJXDEBW.EXE は MDXSERV.EXE の子プロセスとしてだけではなく、単体でも動作できます。

# 第五章 MJX440 の環境設定

MJX440を使用する前に必要な、環境設定の方法について記述しています。

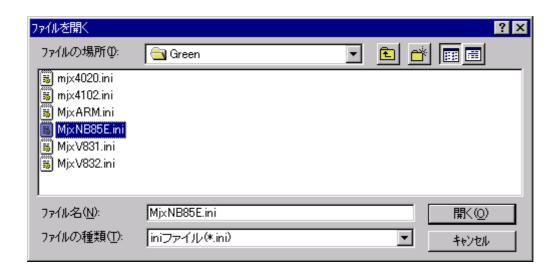

MJX440の環境設定は、コンフィグ支援ツールMJXCFGで行ないます。すべての機器の電源を投入した後、スタートメニューからMJXCFGを起動してください。手順は、次のとおりです。

- 1. スタート メニュー

- 2. プログラム(P)

- 3. MJX Tools

- 4. MjxCfg Config Tool

テンプレートとして MJXNB85E.INI を利用できます。

新たにコンフィグレーションファイルを作成する場合は、新しいファイル名を指定します。

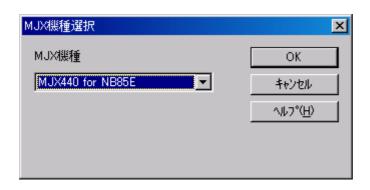

新規のコンフィグレーション ファイルを指定した場合は、次のダイアログ ボックスが表示されます。

MJX の機種から「MJX440 for NB85E」を選択し、**OK**ボタンを押してください。

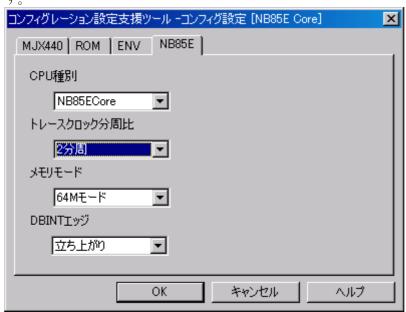

コンフィグレーションファイル指定し、NB85E タブをクリックすると、次のダイアログ ボックスが表示されます。

ダイアログ ボックスが表示されたら、MJX440 やターゲット システムの環境に合わせてフィールドを設定し、**OK** ボタンを押してください。

コンフィグレーション設定項目の詳細は「MJX440/MJX330 MjxCfg User's Manual (Mjxcfg.PDF)」をご覧ください。

# 第六章 ソフトウェアの起動と終了

MJX440を操作するソフトウェアの起動方法と終了方法について記述しています。

【注意】 ソフトウェアを起動する前には必ず「第五章 MJX440 の環境設定」を行ってください。

【注意】MJX440を操作するソフトウェアは、同時にひとつしか実行できません。

#### MULTI を使用する場合

MULTIを使って MJX440 を操作するためには、MULTI 本体を起動した後、次のコマンドで MJXSERV をリモート接続してください。\*1

#### remote mjxserv

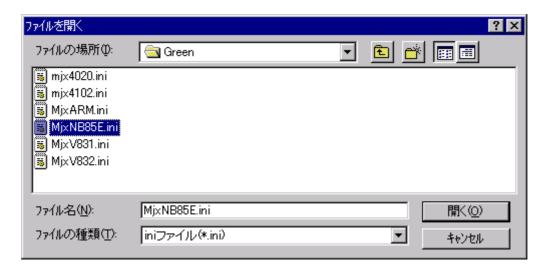

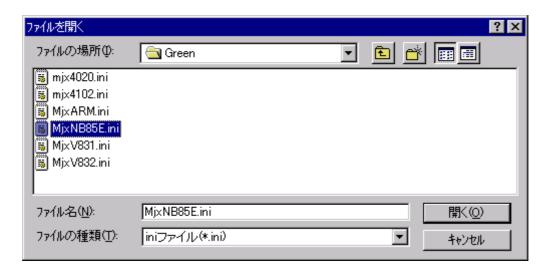

上記コマンドを入力すると、コンフィグレーション ファイルの入力をするための、ダイアログ ボックスが開きます。ここで、「<u>第五章 MJX440の環境設定</u>」で作成したターゲット システム用のコンフィグレーションファイルを指定してください。\*2

<sup>\*1</sup> ビルダから操作する場合は、サーバー名を mjxserv と指定し、 リモート ボタンを押します。

<sup>\*&</sup>lt;sup>2</sup> コンフィグレーション ファイルを指定するダイアログ ボックスで、ファイル名の指定に十数秒以上の時間がかかると、MULTI は「Server Message Timed Out, Terminate Connection?」というメッセージを表示します。このメッセージが表示された場合は、必ず「いいえ」のボタンを押してください。

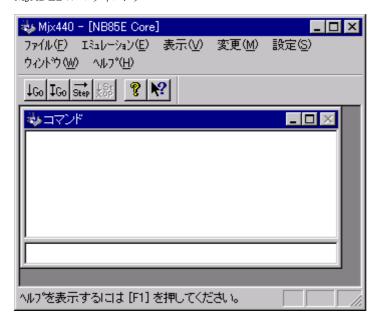

正常にリモート接続できた場合は、MJXDEBW のウィンドウが開きます。

#### MJXDEBW のウィンドウ

コンフィグレーションファイルは、MJXSERV の引数として指定することもできます。次のコマンドは、コンフィグレーション ファイルとして *MjxNB85E. ini* を指定します。

remote mjxserv MjxNB85E.ini

#### MJXDEBW を使用する場合

MJXDEBW を使って MJX440 を操作するためには、スタート メニューから MJXDEBW を起動してください。 手順は、次のとおりです。

- 1. スタート メニュー

- 2. プログラム(P)

- 3. MJX440 Tools

- 4. MJXDEBW Debugger

MJXDEBW が起動されると、コンフィグレーション ファイルの入力をするための、ダイアログ ボックスが開きます。ここで、ターゲット システム用のコンフィグレーション ファイルを指定してください。

MJXDEBW が正常に起動できた場合は、MJXDEBW のウィンドウが開きます。

コンフィグレーション ファイルは、MJXDEBW の引数として指定することもできます。次のコマンドは、コンフィグレーション ファイルとして *MjxNB85E. ini* を指定します。

MJXDEBW MjxNB85E.ini

終了するためには、qコマンドを入力してください。

> q

## 第七章 MJXDEBW コマンド

この章ではデバッガ MJXDEBW のコマンドの使い方について記述しています。

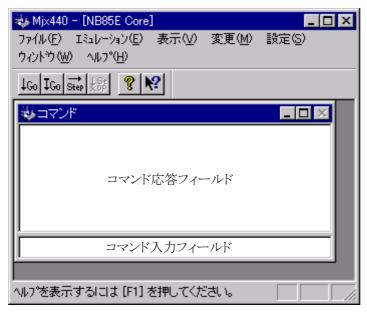

MJXDEBW コマンドは、コマンド ウィンドウ内で実行するコマンドです。 <u>コマンド入力フィールド</u>から入力し、コマンド応答フィールドへ結果を表示します。

図 7-1 MJXDEBW 画面

- コマンド応答フィールドに表示できる行数は、「<u>表示(V) ~ オプション(O) ~ 表示(V)...</u>」メニュー によって変更することができます。

- コマンド入力フィールドはヒストリ バッファを持っています。以前に入力したコマンドは、上下のカー ソル キーによって呼び出すことができます。保持するコマンドの行数は、「<u>表示(V) ~ オプション</u> (O) ~ 表示(V)…」メニューによって変更することができます。

MJXDEBW コマンドの一覧は、次のとおりです。

ABORT ユーザ プログラムを強制停止します

BATCH バッチ ファイルに記述された MJXDEBW コマンドを実行します

BP ブレークポイントを表示/設定/解除します

CLEAR コマンド応答フィールドをクリアします

CONFIG MJX440 の環境を表示/変更します

DUMP メモリの内容を表示します

EVENT イベントを表示/設定します

**EXAMINE** メモリの内容を変更します

FILL メモリの内容をフィルします

FLASH フラッシュ メモリの内容を書き換え、消去します\*1

GO ユーザ プログラムを実行します

HISTORY リアルタイムトレース結果を表示します

INIT MJX440 を再初期化します

JOURNAL コマンド実行結果をファイルへ出力します

LOAD ファイルをメモリヘダウンロードします

MOVE メモリの内容をブロック転送します

<u>OUTTRIG</u> トリガ出力イベントを設定/解除します

PINピンを有効/無効にしますQUITMJXDEBW を終了します

REGISTER レジスタの内容を表示/変更します

<u>SETLOAD</u> ブレークポイント、イベントおよびトレースの設定をファイルから読み出します

SETSAVE ブレークポイント、イベントおよびトレースの設定をファイルへ保存します

STEP ユーザ プログラムをステップ実行します

TRACE リアルタイムトレースのモードを表示/設定します

UNASM メモリの内容を逆アセンブル表示します VERSION ソフトウェアのバージョンを表示します

WAIT ユーザ プログラムが停止するまで待ちます

XPIN 外部トリガ ケーブルの信号の状態を表示/設定します

<sup>\*1</sup> MJX440 for NB85E では、この機能は対応しておりません。

#### コマンド名の省略

コマンド名は、他のコマンド名と区別できる長さまで、省略することができます。

AB ABORTと同じです

CO CONFIGと同じです

CL CLEARと同じです

C エラーです。CONFIGか CLEAR の区別ができません

#### コマンドライン表記のルール

コマンドラインは以下のルールに従って表記します。

[] :省略可能な引数

斜体文字 :変数となる引数

標準文字 :固定の文字引数

{aa|bb|cc} : で区切られた文字列を選択

[xxx...] :xxx が繰り返し指定が可能であることを示す

△ :スペース

表示簡略化のため行末に連続する,(カンマ)は省略可能です。

#### MULTI を使用する場合の注意

次のコマンドは、MULTI のターゲット ウィンドウ内では無視されます。

#### QUIT

次のコマンドは、できれば MULTI のターゲット ウィンドウ内では実行しないでください。

BP/S 命令ソフトウエア ブレークポイントを設定

GO ユーザ プログラムの実行

STEP ユーザ プログラムのステップ実行

REG reg=val レジスタの変更

これらのコマンドはを実行した場合、それ以降、MULTIとMJXSERV間の整合性がとれなくなる危険性があります。ユーザ プログラムの実行制御やレジスタの書き換えは、MULTIのコマンドで行なうようにしてください。

# **ABORT**

ユーザ プログラムを強制停止します

形式:

ABORT 実行中のユーザ プログラムを強制的に停止します。

引数:

例:

GO (ユーザ プログラムを実行します)

ABORT (ユーザ プログラムを強制停止します)

補足:

● 「第八章 <u>エミュレーション(E) ~ 中断(B)</u>」参照。

## **BATCH**

バッチ ファイルに記述された MJXDEBW コマンドを実行します

形式:

BATCH file バッチ ファイル file を一行ずつ読み込み、MJXDEBW コマ

ンドとして実行します。

引数:

file MJXDEBW コマンドが記述されたバッチ ファイル名 (テキスト ファイル)

例:

BAT INIT.TXT (INIT.TXT ファイルをバッチ ファイルとして実行します)

補足:

● BATCH コマンドは、4レベルまでネスティングすることができます。

バッチファイル中の「;」で始まる行は、コメントになります。

● バッチ ファイルの中の QUIT コマンドは、BATCH コマンドのみを終了し、MJXDEBW は終了しません。

● 「第八章 <u>ファイル(F) ~ バッチ(B)...</u>」参照。

### BP

#### ブレークポイントを表示/設定/解除します

#### 形式:

BP [{H|S}] 全ハードウエア(H)/ソフトウエア命令(S)ブレークポイントを表示します。

BP/C  $\{num|*|A*|W*|R*|H*|S*\}$  ブレークポイントを解除します。 BP/D  $\{num|S*\}$  ブレークポイントを無効にします。 T ブレークポイントを有効にします。

BP/{A|W|R} addr, [addrmask],[data],[datamask],[size],[asid]

RW アクセス/WRITE アクセス/READ アクセス

ブレークポイントを設定します。

BP/H addr, [addrmask], [asid]ハードウェア ブレークポイントを設定します。BP/V eventnameイベント ブレークポイントを設定します。BP/N eventnameイベント ブレークポイントを解除します。BP/S addrソフトウエア ブレークポイントを設定します。

#### 引数:

Н

data

S ソフトウェア ブレークポイント指定 ブレークポイント解除 С D ブレークポイント無効 Ε ブレークポイント有効 アクセス ブレークポイント指定 Α W WRITE アクセス ブレークポイント指定 READ アクセス ブレークポイント指定 R ブレークポイント番号指定(10進数) num すべてブレークポイント指定 すべての RW アクセス ブレークポイント指定 Α\* すべての WRITE アクセス ブレークポイント指定 ₩\* すべての READ アクセス ブレークポイント指定 R\* H\* すべてのハードウェア ブレークポイント指定 S\* すべてのソフトウェア ブレークポイント指定 アクセスブレークポイント アドレス指定 (16 進数) addr アクセスブレークポイント アドレスマスク指定 (16 進数) addrmask

ハードウェア ブレークポイント指定

アクセスデータ条件 (省略時はデータ条件の比較なし)

#### 第七章 MJXDEBWコマンド

datamask アクセスデータ条件のマスク(省略時はマスクなし)

size データサイズ {ANY|BYTE|HALF|WORD}から選択。(選択2文字目以降は省略

可)

asid 設定アドレスの ASID 条件(省略時は ASID 条件の比較なし)

eventname EVENT コマンドで設定したイベント識別名

#### 例:

| BP   |      | (ブレークポイントを表示します)                   |

|------|------|------------------------------------|

| BP/C | *    | (すべてのブレークポイントを解除します)               |

| BP/D | S*   | (全ソフトウエア ブレークポイントを無効にします)          |

| BP/E | S*   | (全ソフトウエア ブレークポイントを有効にします)          |

| BP/A | 1000 | (0x1000 番地のメモリ空間にRWアクセス ブレークポイントを  |

|      |      | 設定します)                             |

| BP/H | 2000 | (0x2000 番地にハードウェア ブレークポイントを設定します)  |

| BP/S | 3000 | (0x3000 番地にソフトウェア ブレークポイントを設定します)  |

| BP/V | abc  | (識別名 abc のイベント ブレークポイントを設定します)     |

| BP/N | abc  | (識別名 abc のイベント ブレークポイントを解除します)     |

| BP/S | 1000 | (現在とステートと同じメモリ領域のアドレス 0x1000 番地に命令 |

|      |      | ソフトウェア ブレークポイントを設定します)             |

(-3) L 10 A 1 L + -1 L L

- アクセス/ハードウェア ブレークポイントは、最大 2 個まで設定できます。

- ソフトウェア ブレークポイントは、命令上に最大 128 個まで設定できます。

- ミスアライメントアクセスに対してはデータ条件は無効になります。

- データサイズが ANY の場合、データ条件は無効になります。

- データ条件を省略した場合、データマスク条件は無効になります。

- ソフトウエア ブレークポイントを設定すると、指定したアドレスの命令を実行する直前に ユーザプログラムを停止することができます。

- ソフトウエア ブレークポイントは、RAM 領域に設定することができます。

- 「第八章 設定(S) ~ ブレークポイント(B)...」

# **CLEAR**

コマンド応答フィールドをクリアします

形式:

CLEAR コマンド応答フィールドの表示をすべて消去します。

引数:

例:

CLEAR

補足:

● 「第八章 <u>表示(V) ~ コマンド応答クリア(C)</u>」参照。

### **CONFIG**

MJXDEBW の環境を表示/変更します

形式:

CONFIG 現在設定されている変更可能な MJXDEBW の環境設定を表

示します。

CONFIG/S item=value MJXDEBW の環境設定項目 itemを value に設定します。

引数:

item 環境設定項目、次のいずれかを指定

JCLOCK JTAG クロック

TOPADDR ROM の先頭アドレス

TRCCLK トレースクロック分周比

DBINT EXTIN3 ピンの機能選択

value 環境設定項目に設定する値、

25 または 12.5 JCLOCK の場合 16 進数アドレス TOPADDR の場合 1 または 2 TRCCLK の場合 DIS,LEAD または TRAIL DBINT の場合

DIS EXTIN3 ピンを強制停止信号として使用しない

LEAD EXTIN3 ピンの立ち上がりを強制停止信号として使用する TRAIL EXTIN3 ピンの立ち下がりを強制停止信号として使用する

例:

**CONFIG** (MJXDEBW の環境を表示します)

CONFIG/S JCLOCK=12.5 (JTAG クロックを 12.5MHz に設定します)

CONFIG/S TOPADDR=20000 (ROM の先頭アドレスを 0x20000 に設定します)

CONFIG/S TRCCLK =1 (トレースクロックを1分周に指定します)

CONFIG/S DBINT = DIS (EXIT3 ピンを強制停止信号として使用しません)

補足:

● トレースクロックは CPU クロック1分周または2分周の選択ができます。 MJX440の最大トレース周波数(66MHz)を超えない値を設定してください。

### **DUMP**

メモリの内容を表示します

#### 形式:

$DUMP[/\{B|W|L\}]$  [addr1, [addr2]]

アドレス addr1から addr2 までのメモリの内容を表示します。

#### 引数:

/B 8ビット指定

/W 16 ビット指定

/L 32 ビット指定

*addr1* メモリ表示開始アドレス (16 進数)

*addr2* メモリ表示終了アドレス (16 進数)

#### 例:

DUMP/B1000(0x1000 番地から 64 バイトのメモリを 8 ビットで表示します)DUMP/W2000,20FF(0x2000 から 0x20FF 番地のメモリを 16 ビットで表示します)

DUMP (前回の DUMP コマンドの続きを表示します)

- addr2 省略時は、64 バイト分のメモリを表示します。

- addr1 省略時は、前回の DUMP コマンドの続きを表示します。

- ●ビット指定省略時は、前回のサイズが適用されます。

- ●「第八章 <u>表示(V) ~ メモリ(M)...</u>」参照。

- ●「付録 L <u>V850/ME2 内蔵命令 RAM の取り扱い</u>」参照

### **EVENT**

イベント機能構成と設定されている全イベントを表示/設定します

形式:

EVENT イベント機能構成と設定されている全イベントを表示します。

EVENT/A IP, eventname, addr1[, asid]

命令アドレスイベントを設定します。

EVENT/A IR, eventname, Baddr1, Eaddr1[, asid]

命令アドレス範囲イベントを設定します。

EVENT/A {AP|WP|RP}, eventname, add2r, [data], [datamask], [size][, asid]

RW アクセス(AP)、WRITE アクセス(WP)、READ アクセス(RP)アドレス イベントを設定します。

EVENT/A {AR|WR|RR}, eventname, Baddr2, Eaddr2, [data], [datamask], [size][, asid]

RW アクセス範囲(AR)、WRITE アクセス範囲(WR)、READ アク

セス範囲(RR)アドレス イベントを設定します。

EVENT/D eventname イベントを抹消します。

EVENT/Q eventname, step[, count]

シーケンシャルイベントを設定します。

パスカウントを設定できます。

EVENT/S  $\{1|2|3|4|C\}$ , eventname

シーケンス器 スイッチ イベント(SW1,SW2,SW3,SW4,クリア)

ヘイベントを割り当てます。

EVENT/R  $\{1|2|3|4|C\}$ , eventname

シーケンス器 スイッチ イベント(SW1,SW2,SW3,SW4,クリア)

イベント割当を開放します。

引数:

eventname イベント識別子

addr1 命令アドレス イベント設定アドレス (16 進数)

Baddr1命令アドレス範囲イベント開始設定アドレス(16 進数)Eaddr1命令アドレス範囲イベント終了設定アドレス(16 進数)

addr2 アクセス ブレークポイント設定アドレス (16 進数)

Baddr2

アクセス アドレス範囲イベント開始設定アドレス(16 進数)

Eaddr2

アクセス アドレス範囲イベント終了設定アドレス(16 進数)

#### 第七章 MJXDEBWコマンド

data アクセス データ条件(省略時はデータ条件の比較なし)

datamask アクセス データ条件マスク (省略時は全ビットマスクする。データ条件

省略時は無効)

size データサイズを以下の中から選択(2文字目以降は省略可)

ANY

**BYTE**

HALF

WORD

asid 設定アドレス範囲の ASID 条件(省略時は ASID 条件の比較なし)

step

シーケンス器段数(1~4)

count

パスカウント(省略時は1)

例:

EVENT/A IP,abc,1000 (0x1000 番地に命令アドレスイベントをイベント名 abc で登

録します)

EVENT/A IR,bcd,1000,3000 (0x1000 番地から 0x3000 番地に

命令アドレス範囲イベントをイベント名 bcd で登録します)

EVENT/A RP,cde,1000 (0x1000番地をアクセスブレークポイントとし、READアクセス

アドレスイベントをイベント名 cde で登録します)

EVENT/D abc (イベント名 abc を抹消します)

EVENT/Q def (シーケンシャル イベントをイベント名 def として設定しま

す)

EVENT/S 1.abc (イベント名 abc をシーケンス器スイッチイベント(SW1)に割り

当てます)

EVENT/R 1,abc (イベント名 abc をシーケンス器スイッチイベント(SW1)から割

当を開放します)

- ミスアライメントアクセスに対してはデータ条件は無効になります。

- データサイズが ANY の場合、データ条件は無効になります。

- データ条件を省略した場合、データマスク条件は無効になります。

- イベントを抹消する場合、チャンネル割当が行われている場合は、チャンネルが開放されます。シーケンシャル イベントの場合は、シーケンシャル器が無効になります。

● シーケンシャル イベントの設定は、「EVENT/A」コマンドでシーケンス器スイッチイベント割り 当てを行わなければなりません。

シーケンス器 スイッチ イベントの割り当ては、

シーケンス器段数が1段のときはSW4が有効になります。

シーケンス器段数が2段のときはSW4、SW3が有効になります。

シーケンス器段数が3段のときはSW4,SW3,SW2が有効になります。

シーケンス器段数が4段のときはSW4,SW3,SW2,SW1が有効になります。

このコマンドでは実際にイベントチャンネルの割り当てが行われます。

- イベントは、有効/無効あわせて最大 128 個のイベントを設定できます。

- 関連コマンド TRACE, BP, OUTTRIG

- 「第八章 設定(S) ~ イベント(E)...」参照。

#### 1 イベント識別名のルール

イベント識別名はカンマ、スペース、タブを除く印字可能半角文字から構成します。 最大 32 文字まで指定できます。

#### 2 イベントチャンネルの占有:

イベントが設定できるハードウエア(イベントチャンネル)は有限です。

「EVENT/S [IP|AP|WP|RP|IR|AR|WR|RR]」コマンドでは各イベントはハードウエアのイベントチャンネルに対して割り当ては行われません。

BP/V

EVENT/S

TRACE/I [BE|EE|ME|IE]

OUTTRIG/S

コマンドが発行された時点でハードウエアのイベントチャンネルに対して割り当てが行われます。イベントチャンネルは命令系とアクセス系に分かれており、各チャンネル数は

EVENT イベント機能構成表示コマンドで知ることができます。

範囲イベントはイベントチャンネルを2チャンネル占有します。

## EXAMINE

メモリの内容を変更します

形式:

EXAMINE/{B|W|L} addr=data1[, data2...]

アドレス addr のメモリをデータ data1[,data2...]に変更しま

す。

引数:

/B 8 ビット指定 /W 16 ビット指定 /L 32 ビット指定

addr メモリ変更開始アドレス (16 進数)

data1, data2 メモリ変更データ (16 進数)

例:

EXAMINE/B 1000=55 (0x1000 番地のメモリを 8 ビットデータ 0x55 に変更します)

EXAMINE/W 3000=1,2,3 (0x3000 番地からのメモリを 16 ビットデータ 0x0001、0x0002、

0x0003 に変更します。)

- ●「第八章 <u>表示(V) ~ メモリ(M)…</u>」参照。

- ●「付録 L V850/ME2 内蔵命令 RAM の取り扱い」参照。

## FILL

メモリの内容を変更します

#### 形式:

FILL/{B|W|L} addr1,addr2,data

アドレス addr1 から addr2 までのメモリを、データ data でフィルします。

#### 引数:

/B 8 ビット指定

/W 16 ビット指定

/L 32 ビット指定

addr1 メモリ フィル開始アドレス (16 進数)

addr2 メモリ フィル終了アドレス (16 進数)

*data* フィル データ (16 進数)

#### 例:

**FILL/B 0,3FF,FF** (0x0 から 0x3FF 番地のメモリを 8 ビットデータ 0xFF でフィルし

ます)

FILL/W 1000,1FFF,0 (0x1000から0x1FFF番地のメモリを16ビットデータ0x0000で

フィルします)

- ●8M バイト以上のフィルはできません。(制限事項)

- ●「第八章 <u>変更(M) ~ フィル(F)...</u>」参照。

- ●「付録 L V850/ME2 内蔵命令 RAM の取り扱い」参照。

### **FLASH**

フラッシュ メモリの内容を書き換え 消去します

形式:

FLASH[/WRITE|/UPDATE] file\_name[,[device\_type,acc\_s\_bus\_width]]

フラッシュメモリの内容を書き戻す。

FLASH[/ERASEONE|/ERASEALL] addr[,[device\_type,2 \_\_\_\_\_bus\_wrd \_\_]

フラッシュ メモリの内外 消井 よ

/WRITE フラッシュ メモリにデータを書き込みます。

/UPDATE フラッシュ メモリのデータを更新しましたクタ単位で消去後、

書き込み)

/ERASEONE フラッシュ メー、の内容をセクッ・位に消去します

/ERASEALL フラッシュ メモリの内名 (チッフ 草立に)消去します

引数:

file\_name ダウンロードするショイル名 (書きみデータ)

addr 消去アドレニ (16 進票: " 指定。 絶対アドレスです。 先頭からのオフセッ

トではあり。

device\_type ブラッシュ デバイメニ (省略時は、コンフィグレーション設定値を使用)

access\_bus\_wic ニアクセス / (省略時は、コンフィグレーション設定値を使用)

1 ジイトアクロ

2 2 バイ クセス

バイト アクセス

例:

FLASH/WRITE bad.hex,,2 (load.hex ファイルの内容をコンフィグレーション設定値で指定されたフラッシュ デバイスへ 2 バイト単位で書き込む)

FLASH FASEONE BT \$240,AM29F080B

(AM29F080B の BFC00040(16 進) のアドレスに該当するセクタ

を消去)

- オプション省略時は、/WRITE を既定値とします。

- ファイル形式 (MJX バイナリ、Sレコード、インテル HEX、COFF 形式)は自動認識 れます。

- {MjxDebw.exe の格納ディレクトリ}¥zax\_mjx¥flash¥device の下に{device\_smallat ファゴルを作成して、デバイス情報定義ファイルが存在する必要があります。

ファイル レイアウトは、「付録」フラッシュ メモリ デバイス情報定義 スーパーレイアウト」を参照してください。

- ソフトウェア ブレークポイントは全てクリアされます。

- ロックビットのセット・リセットの機能があるフラッシュ デバイモでは、エック デージクリアされている必要があります。

- 本機能が対応するフラッシュ メモリの一覧は、「付録 K 出 スフラップ リー覧」にあります。

- 本機能はターゲット ボード上の RAM に書き込みプーグラム本 フラッシュ メモリ デバイス情報、 更新データ (セクタ単位) をロードして実行されま 実行に必要なメモリ容量は、18 K バイト + (フラッシュ テーゴスの全セクタ数 x 8 バイト) + 更新されるセクタ (複数あるときはそのうちの最大) サイス・ト

- 本機能を使用する場合、事前にRAMを使用可能にする必要があります。(手順はCPU及びターゲットボードに依存します。)

- 本機能を使用する場合、フラッシュ領域 するキャッシュ設定を無効にする必要があります。

- 「第八章 MJXDEBW メニューコマン・」参照。

GO

ユーザ プログラムを実行します

形式:

GO [addr] アドレス addr からユーザ プログラムを実行します。

引数:

addr ユーザ プログラム開始アドレス (16 進数)

例:

GO 1000 (0x1000 番地からユーザ プログラムを実行します)

GO (現在の PC からユーザ プログラムを実行します)

補足:

● ユーザ プログラムがプレークポイントなどで停止しない場合、WAIT あるいは ABORT コマンドで強制終了させます。(タイムアウトはありません。)

- MULTI のターゲット ウィンドウ内では、実行しないでください。

- *addr* 省略時は、現在の PC から実行します。

- 「第八章 <u>エミュレーション(E) ~ 実行(G)...</u>」参照。

- 「第八章 <u>エミュレーション(E)</u> ~ 再スタート(R)」参照。

### HISTORY

リアルタイム トレース結果を表示します

形式:

HISTORY リアルタイムトレース結果が格納されている、パケット番号の

範囲を表示します。

HISTORY/P [start[,end]] パケット番号 start から end までのリアルタイム トレース結果

を、パケット単位で表示します。

HISTORY/D [start[,end]] パケット番号 start から end までのリアルタイム トレース結果

を、逆アセンブルで表示します。

引数:

start 表示開始パケット番号 (10 進数)

end 表示終了パケット番号 (10 進数)

例:

HISTORY (リアルタイム トレース結果が格納されている、パケット番号の

範囲を表示します)

HISTORY/P -10,0 (パケット番号-10から0までのリアルタイムトレース結果を、パ

ケット単位で表示します)

HISTORY/D 0.70 (パケット番号 0 から 70 までのリアルタイム トレース結果を、逆

アセンブルで表示します)

補足:

● *end*省略時は、16 パケット分を表示します。

● *start* 省略時は、前回の HISTORY コマンドの続きを表示します。

● *start* と *end* は、パケット番号 0 を起点とするオフセットで指定します。

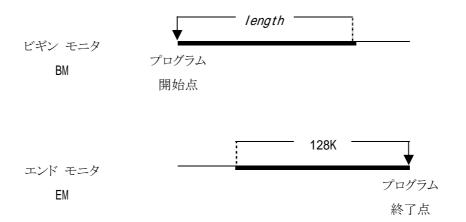

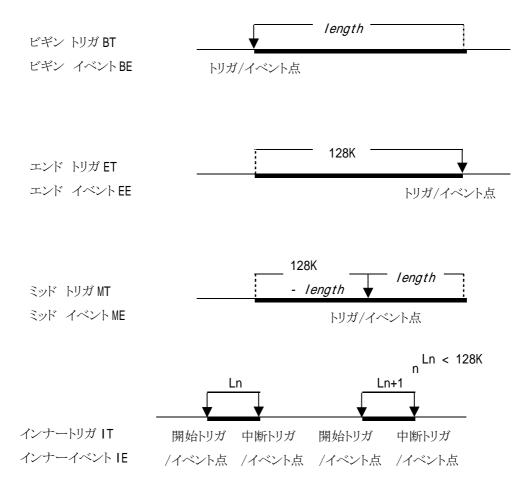

トレース条件により、パケット番号0の点は、次のように異なります

ビギン モニタ プログラム開始点 エンド モニタ プログラム終了点 ビギン トリガ/ビギンイベント トレース トリガ点 エンド トリガ/エンドイベント トレース トリガ点 トレース トリガ点 インナートリガ/インナーイベント トレース開始トリガ点

「第八章 表示(V) ~ トレース結果(T)...」参照。

# INIT

MJX を再初期化します

形式:

INIT MJX を再初期化します。

補足:

● ターゲットシステムの CPU もリセットされます。

● 「第八章 <u>エミュレーション(E) ~ 初期化(I)</u>」参照。

### **JOURNAL**

コマンド実行結果をファイルへ出力します

形式:

JOURNAL[/{A|W}] file[, mode[, echo]]

コマンド実行結果をファイル file へ出力するようにします。

JOURNAL/E ファイルへの出力を終了し、ファイルをクローズします。

引数:

/A 追記出力指定

/W 新規出力指定(省略時)

file 出力ファイル名指定

*mode* 出力モード指定

IN コマンドのみ出力

OUT コマンド実行結果のみ出力

ALL(省略時) コマンドとコマンド実行結果を出力

echo エコー モード指定

OFF ファイルへ出力する内容は画面に表示しない ON (省略時) ファイルへ出力する内容を画面にも表示する

例:

JOURNAL TEST.TXT (コマンド実行結果をTEST.TXT ファイルへ出力するようにしま

す)

JOURNAL/E (ファイルへの出力を終了し、ファイルをクローズします)

JOURNAL/A TEST.TXT (コマンド実行結果をファイル TEST.TXT へ追記出力するように

します)

- /Wを指定し、かつ同名のファイルが存在する場合、そのファイルの内容は失われます。

- 「第八章 ファイル(F) ~ ジャーナル開始(S)...」参照。

- 「第八章 ファイル(F) ~ ジャーナル停止(E)」参照。

### LOAD

ファイルをメモリヘダウンロードします

形式:

LOAD *file*[, *offset*] MJX バイナリ\*1、S レコード、インテルヘキサ、または COFF 形

式のファイル fileをメモリヘダウンロードします。

LOAD/R file[, offset] MJX バイナリ ファイル fileをエミュレーション メモリ経由でメ

モリヘダウンロードします。より高速にダウンロードを行うことが

できます。

引数:

*file* ダウンロードするファイル名 *offset* オフセット アドレス (省略時 0)

例:

LOAD PROG1.ABS (ファイル PROG1.ABS をメモリヘダウンロードします)

LOAD PROG1.ABS,2000 (ファイル PROG1.ABS をメモリヘダウンロードします)

LOAD/R PROG2.MJX (ファイル PROG2.MJX をエミュレーション メモリ経由でメモリへ

ダウンロードします)

補足:

● ファイル形式は、自動認識されます。

- ファイル名の拡張子を省略した場合は、.mjx が補完されます。

- LOAD/R コマンド時、MJX バイナリ ファイルの中に、エミュレーション メモリを指すレコードがある場合、正しくダウンロードできません。

- /R 指定でダウンロードを行った場合エミュレーションメモリの内容は破壊されます。

- 「第八章 エミュレーション(E) ~ ダウンロード(L)…」参照。

- 「付録 L V850/ME2 内蔵命令 RAM の取り扱い」参照。

<sup>\*1</sup> MJX バイナリ ファイルについては「第八章 高速ダウンロード」を参照してください。

### MOVE

メモリの内容をブロック転送します

#### 形式:

MOVE[/{B|W|L}] addr1, addr2, addr3

アドレス *addr1*から *addr2*までのメモリを *addr3*ヘブロック転送します。

#### 引数:

/B 8ビット指定

/W 16 ビット指定

/L 32 ビット指定

*addr1* 転送元メモリ開始アドレス (16 進数)

addr2 転送元メモリ終了アドレス (16 進数)

addr3 転送先メモリ アドレス (16 進数)

#### 例:

MOVE 1000,10FF,2000 (0x1000 から 0x10FF 番地のメモリを 0x2000 番地へブロック転送します)

- 8M バイト以上のブロック転送はできません。(制限事項)

- サイズ省略時は8ビット設定が選択されます。

- 転送元領域と転送先領域が重なっている場合の結果は不定です。

- 「第八章 <u>変更(M) ~ 移動(M)...</u>」参照。

# OUTTRIG

トリガ出力イベントを設定/解除します

形式:

OUTTRIG/Seventnameトリガ出力イベントを設定します。OUTTRIG/Reventnameトリガ出力イベントを解除します。

引数:

eventname イベント識別名

例:

OUTTRIG/Sabc(イベント abc をトリガ出力イベントとして設定します)OUTTRIG/Rabc(イベント abc をトリガ出力イベントから解除します)

- トリガ出力のイベントは、ターゲットCPUにイベントトリガ出力機能が実装されている場合 のみ有効です。

- 「第八章 <u>設定(S) ~ イベント(E)...</u>」参照。

# PIN

ピンを有効/無効にします

形式:

PIN ピンの有効/無効の状態を表示します。

PIN *pinname*={EN|DI} ピン *pinname* の入力信号マスク機能を設定します。

引数:

pinname マスク可能なピン名、次のいずれかを指定

NMIO

NMI1

NMI2

HLDRQ

ST0PZ

**RESETZ**

DBINT

INT00

INT01

.

•

.

INT63

EN 設定を有効にする

DI 設定を無効にする

例:

PIN (ピンの有効/無効の状態を表示します。)

PIN NMIO=DI (ピン INMIO の入力信号マスク機能の設定を無効にします。)

# QUIT

MJXDEBW を終了します

形式:

**QUIT** MJXDEBW を終了します。

補足:

● バッチ ファイルの中の QUIT コマンドは、BATCH コマンドのみを終了し、MJXDEBW は終了しません。

# REGISTER

レジスタの内容を表示/変更します

形式:

RESISTER レジスタの内容をを表示します。

RESISTER reg=data レジスタ regをデータ data に変更します。

引数:

reg レジスタ名指定

「付録 G <u>レジスタ名一覧</u>」を参照してください

data レジスタ変更データ (16 進数)

例:

REGISTER PC=2000 (PC を 0x2000 に変更します)

補足:

● MULTIを使用している場合は、レジスタを変更しないでください。

● 「第八章 <u>表示(V) ~ レジスタ(R)</u>」参照。

# **SETLOAD**

ブレークポイント、イベントおよびトレースの設定をファイルから読み出します

形式:

SETLOAD filename ブレークポイント、イベントおよびトレースの設定をファイルから

読み出します。

引数:

filename 読み出すファイル名

例:

SETLOAD abc.mjs (abc.mjs ファイルを読み出します)

補足:

● 「第八章 設定(S) ~ 設定の読出(L)…」参照。

# **SETSAVE**

ブレークポイント、イベントおよびトレースの設定をファイルから保存します

形式:

SETSAVE filename ブレークポイント、イベントおよびトレースの設定をファイルへ

保存します。

引数:

filename 保存するファイル名

例:

SETSAVE abc.mjs (abc.mjs ファイルを保存します)

補足:

● 同じ名前のファイルが存在する場合、上書きします。

● 「第八章 <u>設定(S) ~ 設定の保存(S)...</u>」参照。

## **STEP**

ユーザ プログラムをステップ実行します

形式:

STEP [num] ユーザ プログラムを num 回ステップ実行します

引数:

num ステップ実行回数指定 (10 進数、省略時は 1)

例:

STEP (ユーザ プログラムを 1 回ステップ実行します。) STEP 10 (ユーザ プログラムを 10 回ステップ実行します。)

補足:

● MULTIを使用している場合は、レジスタを変更しないでください。

● 「第八章 エミュレーション(E) ~ ステップ(S)」参照。

● 「第八章 <u>エミュレーション(E) ~ N-ステップ(N)...</u>」参照。

## **TRACE**

リアルタイム トレースの全トレース条件を表示します

形式:

TRACE トレース条件をすべて表示します。

引数:

例:

TRACE (トレース条件をすべて表示します)

補足:

● 「第八章 <u>設定(S) ~ トレース(T)…</u>」参照。

## TRACE/A

RW/WRITE/READ データ トレースポイントを設定します

形式:

TRACE/A {A|W|R}, addr[, addrmask[, asid]]

RW デーg(A),WRITE デーg(W),READ(R)データ トレースポイントを設定します。

引数:

addr データ トレースポイント設定アドレス(16 進数)

addrmask データ トレースポイント設定アドレスマスク (16 進数。省略時はマスクな

L)

asid 設定アドレスの ASID 条件(省略時は ASID 条件の比較なし)

例:

TRACE/A W,1000

(0x1000番地へのWRITEアクセスをデータトレースポイントとして設定します)

補足:

- 命令トレース停止時にはデータトレースはエンドモニタモードで実行します。データトレースポイントは最大2点まで設定できます。

- *addr* の有効範囲は A27-A2 です。

- *addrmask*の有効範囲はA9-A2です。

- 「第八章 <u>設定(S) ~ トレース(T)...</u>」参照。

## TRACE/C

データ トレースポイントを解除します

形式:

TRACE/C addr データトレースを解除します。

TRACE/C \* すべてのデータトレースを解除します。

引数:

*addr* データトレースポイント設定アドレス(16 進数)

\* すべてのデータ トレースポイント

例:

TRACE/C \* (すべてのデータ トレースポイントを解除します。)

補足:

● 「第八章 設定(S) ~ トレース(T)…」参照。

### TRACE/M

トレースモードおよびトレース要因を設定します

形式:

TRACE/M mode[, mask] トレースモードおよびトレース要因の設定をします

引数:

*mode* トレースモードを指定します。

RT:通常モード

FL:完全モード

mask トレースするトレース要因をビット毎に16進数で指定します。

800000:CTRET 命令(分岐元 PC)

000800:CTRET 命令(分岐先 PC)

400000:DISPOSE 命令(分岐元 PC)

000400:DISPOSE 命令(分岐先 PC)

200000:SWITCH 命令(分岐元 PC)

000200:SWITCH 命令(分岐先 PC)

100000:CALLT 命令(分岐元 PC)

000100:CALLT 命令(分岐先 PC)

080000:条件分岐命令(条件成立)による分岐(分岐元 PC)

000080:条件分岐命令(条件成立)による分岐(分岐先 PC)

040000:条件分岐命令(条件不成立)による分岐(分岐元 PC)

000040:条件分岐命令(条件不成立)による分岐(分岐先 PC)

020000:JARL 命令(分岐元 PC)

000020:JARL 命令(分岐先 PC)

010000:JR 命令(分岐元 PC)

000010:JR 命令(分岐先 PC)

008000:JMP 命令(分岐元 PC)

000008:JMP 命令(分岐先 PC)

004000:RETI 命令(分岐元 PC)

000004:RETI 命令(分岐先 PC)

002000:例外発生(分岐元 PC)

000002:例外発生(分岐先 PC)

.

001000:割り込み発生(分岐元 PC)

000001:割り込み発生(分岐先 PC)

省略時は標準設定(下記参照)になります。

#### <標準設定>

000800:CTRET 命令(分岐先 PC)

000400:DISPOSE 命令(分岐先 PC)

000200:SWITCH 命令(分岐先 PC)

000100:CALLT 命令(分岐先 PC)

080000:条件分岐命令(条件成立)による分岐(分岐元 PC)

040000:条件分岐命令(条件不成立)による分岐(分岐元 PC)

000008:JMP 命令(分岐先 PC)

000004:RETI 命令(分岐先 PC)

002000:例外発生(分岐元 PC)

000002:例外発生(分岐先 PC)

001000:割り込み発生(分岐元 PC)

000001:割り込み発生(分岐先 PC)

例:

TRACE/M RT, 008000

(トレース モードを通常モードに、トレース要因を JMP 命令(分

岐元PC)に設定します)

#### 補足:

- 完全トレース モードでは、データ トレースポイントは無効になります。

- 標準設定で設定されるトレース要因が1つでも欠けると逆アセンブル モードでのトレース結果表示はできません。

- トレース要因を増やすとリアルタイムモード時、オーバーフローが発生しやすくなりますが、 逆アセンブラ表示時のオーバーフロー発生による実行アドレス喪失からの復帰が早くな ります。

- 「第八章 設定(S) ~ トレース(T)…」参照。

### TRACE / I

実行トレース条件を設定します

形式:

TRACE/IBM, length実行トレース条件をビギン モニタに設定します。TRACE/IEM実行トレース条件をエンド モニタに設定します。TRACE/IBT, addr[, asid]実行トレース条件をビギン トリガに設定します。TRACE/IET, addr[, asid]実行トレース条件をエンド トリガに設定します。

TRACE/I MT, addr, length[, asid]

実行トレース条件をミッドトリガに設定します。

TRACE/I IT, Saddr, Eaddr[, [Sasid], [Easid]]

実行トレース条件をインナートリガに設定します。

TRACE/I BE, eventname1[, eventname2...]

実行トレース条件をビギン イベントに設定します。

TRACE/I EE, eventname1[, eventname2...]

実行トレース条件をエンド イベントに設定します。

TRACE/I ME, length, eventname1[, eventname2...]

実行トレース条件をミッドイベントに設定します。

TRACE/I IE, Seventname, Eeventname

実行トレース条件をインナー イベントに設定します。

TRACE/I DI 実行トレース条件を中止します。

引数:

addr トリガ アドレスを指定

asid トリガ アドレスの ASID 条件 (省略時は ASID 条件なし)

Saddr インナートリガ条件のトレース開始アドレスを指定 インナートリガ条件のトレース中断アドレスを指定

Sasid インナートリガ条件のトレース開始アドレスのASID条件を指定(省略時は

ASID 条件の比較なし)

Easid インナートリガ条件のトレース中断アドレスのASID条件を指定(省略時は

Sasidと同じ)

eventnameN トリガ イベントを指定

SeventnameNインナー イベント条件のトレース開始イベントを指定EeventnameNインナー イベント条件のトレース中断イベントを指定Iengthトレース ワード長を指定(省略時は最大 131072 ワード)

例:

TRACE/I BT, 1000 (実行トレース条件をビギン トリガに、トレース トリガのアドレスを 0x1000 に設定します)

#### 補足:

- MJX440 のトレース バッファの長さは 128K ワードです。1ワードに N-Wire からのトレースデータを8bit 入れることができます。

N-Wire のトレース パケットは可変長であり、指定長のトレース バッファに何パケット入るかは予測できません。

- トレース スタートと分岐が同時に発生した場合、分岐パケットが出ません。 この場合、トレース 逆アセンブラ表示が実行アドレス喪失状態になります。 トレース スタートと分岐命令が重ならないようなアドレスを推奨します。 また、トレース スタートと割り込みが重ならないように制御することはできません。 この場合、トレース 逆アセンブラ表示が正しく行われません。 トレース スタートアドレスは各実行トレース条件ごとに以下のようになっています。

・IT, IE: トレース開始アドレス/トレース開始イベント

•その他:プログラム開始アドレス

- BT,ET,MT,BE,EE,ME の各実行トレース条件ではトリガ/イベント点で MJX440 の EXTERNAL コネクタの TRGOUT 端子から LOW レベルが出力されます。 IT,IE では、TRGOUT は出ません。

- BE, EE, ME モードではトリガ イベントを複数設定できます。最初に発生したイベントがトリガになります。また、IE モードでもイベントの複数設定が可能ですが、コマンドラインでは入力することができません。イベント設定ダイアログボックスで設定してください。

- 「第八章 設定(S) ~ トレース(T)…」参照。

#### トレース範囲:

## TRACE/R

全トレース条件を無効にします

形式:

TRACE/R トレース条件をすべて無効にします。

引数:

例:

TRACE/R (トレース条件をすべて無効にします)

補足:

● 「第八章 <u>設定(S) ~ トレース(T)...</u>」参照。

## **UNASM**

メモリの内容を逆アセンブル表示します

形式:

UNASM [addr[, count]] アドレス addr から count 命令分のメモリの内容を逆アセンブル

表示します。

引数:

addr 逆アセンブル表示メモリ開始アドレス (16進数)

count 逆アセンブル表示命令数 (10 進数、省略時 16)

例:

UNASM 1000 (0x1000 番地から 16 命令分のメモリを逆アセンブル表示しま

す)

UNASM (前回の UNASM コマンドの続きを表示します)

補足:

● count 省略時は、16 命令分のメモリを逆アセンブル表示します。

- addr省略時は、前回のUNASMコマンドの続きを表示します。

- 「第八章 <u>表示(V) ~ 逆アセンブル(D)...</u>」参照。

- 「付録 L <u>V850/ME2 内蔵命令 RAM の取り扱い</u>」参照。

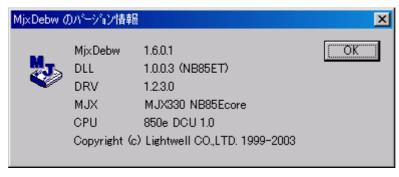

## **VERSION**

ソフトウエアのバージョンを表示します

形式:

VERSION 次のバージョン情報を表示します。

MjxDebw MJXDEBW.EXE ソフトウェアのバージョン

DLL CPU 依存 DLL ライブラリのバージョン

DRV デバイス ドライバのバージョン

MJX エミュレータのバージョン

CPU CPU の種類

DCU のバージョン

例:

**VERSION**

補足:

●「第八章 <u>ヘルプ(H) ~ MJXDEBW のバージョン情報(A)</u>」参照。

## WAIT

ユーザ プログラムが停止するまで待ちます

形式:

WAIT [time] ユーザ プログラムが停止するまで待ちます。指定時間内に停

止しない場合は、ユーザ プログラムを強制停止します。

引数:

time 待ち時間 (10 進数、単位ミリ秒、省略時は∞)

例:

GO (ユーザ プログラムを実行します)

WAIT 1000 (ユーザ プログラムが停止するまで待ちます。1 秒以内に停止

しない場合は、ユーザ プログラム強制停止します)

補足:

● 待ち時間はミリ秒単位で指定できますが、実際の精度は百ミリ秒程度です。

• バッチファイル内で使用してください。

## **XPIN**

外部トリガ ケーブルの信号の状態を表示/設定します

形式:

XPIN 外部トリガ ケーブルの信号の状態を表示します。

XPIN ch, level 外部トリガ ケーブルの出力信号 ch をレベル level に設定し

ます。

引数:

ch 外部トリガ ケーブルの出力信号のピンの指定

1 EXTOUT1

2 EXTOUT2

level 出力ピンのレベル指定

0 LOW レベル

1 HIGH レベル

例:

XPIN (外部トリガ ケーブルの信号の状態を表示します。)

XPIN 1,0 (外部トリガ ケーブルの出力信号 EXTOUT1 をLOW レベルに

設定します。)

補足:

■ 出力信号は負論理です。

## 第八章 MJXDEBW メニューコマンド

この章ではデバッガ MJXDEBW のメニュー コマンドの使い方について記述しています。

メニュー コマンドを使用すると、「第七章 MJXDEBW コマンド」に相当することを、メニューから実行させることができます。各メニューには、次のようにコマンドが割り当てられています。

#### 🗞 Mjx440 - [NB85E Core]

ファイル(E) エミュレーション(E) 表示(V) 変更(M) 設定(S) ウィントウ(W) ヘルプ(H)

図8-1 MJXDEBW のメニューバー

ファイル(F) ファイル メニューには、ファイルからコマンドを読み込みバッチ処理を行なう

コマンド、コマンドの実行結果をファイルに残すジャーナル処理のコマンドな

どが割り当てられています。

エミュレーション(E) エミュレーション メニューには、ユーザ プログラムの実行制御、プログラム

のダウンロード、初期化コマンドが割り当てられています。

表示(V) 表示メニューには、次のウィンドを表示するためのコマンドが含まれています

メモリ ウィンドウ、レジスタ ウィンドウ、逆アセンブル ウィンドウ、トレース結

果ウィンドウ。

変更(M) メモリ/レジスタなどを変更するためのコマンドが割り当てられています。

設定(S) ブレークポイントやトレース モードを設定するためのコマンドが割り当てられ

ています。

ウィンドウ(W) ウィンドウの表示形式を変更するためのコマンドが割り当てられています。

(Windows 準拠)

ヘルプ(H) MIXDEBW のバージョン情報を表示するためのコマンドが割り当てられてい

ます。

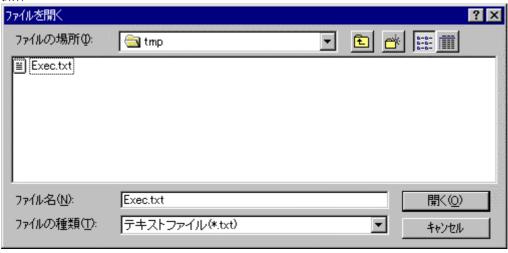

# ファイル(F) ~ バッチ(B)...

BATCH

#### 機能:

バッチ ファイルに記述された MJXDEBW コマンドを連続して実行します。

#### 操作:

ダイアログ ボックスで、ファイル名を指定し、「開く」ボタンを押してください。

#### 補足:

● 「第七章 BATCH」参照。

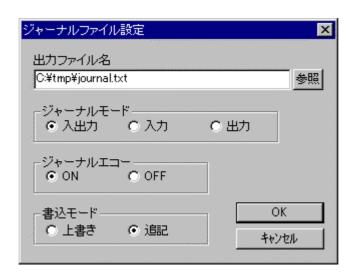

## ファイル(F) ~ ジャーナル開始(S)...

JOURNAL

#### 機能:

コマンド実行結果をファイルへ出力する、ジャーナル機能を開始します。

#### 操作:

ダイアログ ボックスで、<u>出力ファイル名</u>、<u>ジャーナル モード、ジャーナル エコー</u>、<u>書き込みモードを指定し、「OK」ボタンを押してください。</u>

#### 補足:

● 「第七章 JOURNAL」参照。

# ファイル(F) ~ ジャーナル停止(E)

JOURNAL/E

#### 機能:

ジャーナル機能を終了します。

#### 補足:

● 「第七章 <u>JOURNAL</u>」参照。

# ファイル(F) ~ トレース結果(T)...

HISTORY

機能:

トレース結果をファイルへ出力します。

補足:

● 現在未対応の機能です。

# エミュレーション(E) ~ 実行(G)...

GO addr

Ctrl+G

#### 機能:

プログラムの実行を開始するアドレスを指定してユーザ プログラムを実行します。

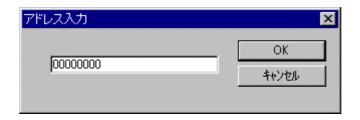

#### 操作:

ダイアログ ボックスで、プログラムの実行を開始する<u>アドレス(16</u> 進数)を指定し、「OK」ボタンを押してください。

#### 補足:

● 「第七章 <u>GO</u>」参照。

## エミュレーション(E) ~ 再スタート(R)

GO

F5

#### 機能:

現在のPCのアドレスからユーザ プログラムを実行します。

#### 補足:

● 「第七章 GO」参照。

# エミュレーション(E) ~ 中断(B)

**ABORT**

Ctrl+B

機能:

ユーザ プログラムを強制停止します。

補足:

● 「第七章 <u>ABORT</u>」参照。

## エミュレーション(E) ~ ステップ(S)

STEP

F10

機能:

ユーザ プログラムをステップ実行します。

補足:

● 「第五章 <u>STEP</u>」参照。

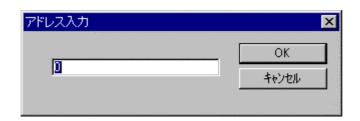

# エミュレーション(E) ~ N-ステップ(N)...

STEP num

Ctrl+S

#### 機能:

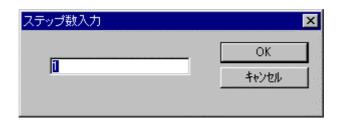

ユーザ プログラムを指定回数分ステップ実行します。

#### 操作:

ダイアログ ボックスで、ステップ実行回数(10進数)を指定し、「OK」ボタンを押してください。

#### 補足:

● 「第五章 STEP」参照。

# エミュレーション(E) ~ ダウンロード(L)...

LOAD

Ctrl+L

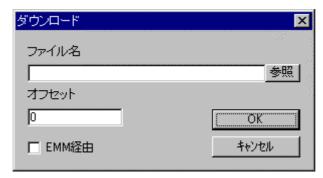

#### 機能:

MJX バイナリ $^{*1}$ 、S レコード、インテル HEX、または COFF 形式のファイル *file* をメモリヘダウンロードします。

#### 操作:

ダイアログ ボックスで、ファイル名、オフセット、EMM 経由を指定し、「OK」ボタンを押してください。

#### 補足:

- ファイル形式は、自動認識されます。

- EMM 経由をONにするとエミュレーションメモリの内容は破壊されますが より高速にダウンロードが実行できます。

- 「第七章 LOAD」参照。

- 「付録 L V850/ME2 内蔵命令 RAM の取り扱い」参照。

<sup>\*1</sup> MJX バイナリ ファイルの作成方法については「第九章 高速ダウンロード」を参照してください。

# エミュレーション(E) ~ 初期化(I)

INIT

機能:

MJX を再初期化します。

補足:

● 「第七章 <u>INIT</u>」参照。

# エミュレーション(E) ~ フラッシュメモリ(F) ~ 書込(W)...

FLASI RITE

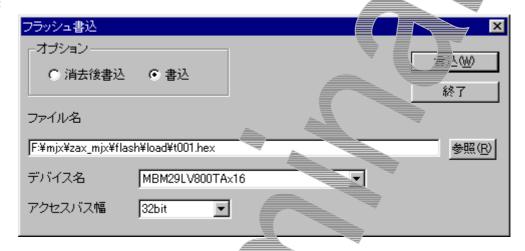

#### 機能:

MJX バイナリ、Sレコード、インテル HEX、または COFF 形式ファイルを ブッシュ メモリへ 込みます。

#### 操作:

ダイアログ ボックスで、ファール デバイス 、アクセス バス幅を指定して、「書込」ボタンを押してください。

#### 補足:

- ファイル形式は自動、識されます。

- 「第4 = 1 ASH」参照。

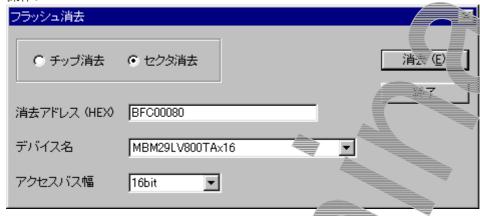

# エミュレーション(E) ~ フラッシュメモリ(F) ~ 消去(E)...

FLASH/ERASEALL

#### 機能:

指定された消去アドレスに該当するフラッシュメモリをセクタ消去、またによっプ消去します。

#### 操作:

ダイアログ ボックスで<u>消去 デンタ デバラ名、アクセス バス幅</u>を指定して、「消去」ボタンを 押してください。

#### 補足:

● 「第十章 <u>FLAS</u>」。照。

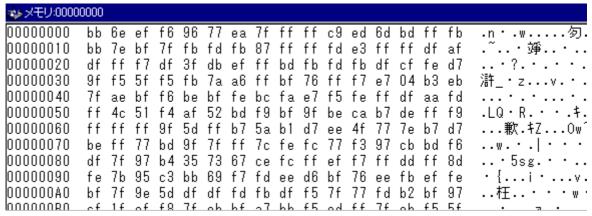

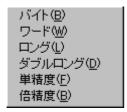

## 表示(V) ~ メモリ(M)...

**DUMP**

機能:

メモリの内容を表示する、メモリウィンドウを開きます。

操作:

ダイアログ ボックスで、メモリ表示を開始する<u>アドレス(16</u> 進数)を指定し、「OK」ボタンを押してください。

新しくメモリウィンドウが表示されます。

メモリ ウィンドウ内で、マウスの右ボタンを押すと、ポップアップ メニューが表示され、表示形式を変更することができます。

#### 第八章 MJXDEBW メニューコマンド

#### 補足:

- メモリ ウィンドウは複数開くことができます。開くことができるウィンドウ個数は、「<u>表示(V) ~</u> オプション(O) ~ 表示(V)...」メニューで変更することができます。

- 「第七章 <u>DUMP</u>」参照。

- 「付録 L V850/ME2 内蔵命令 RAM の取り扱い」参照。

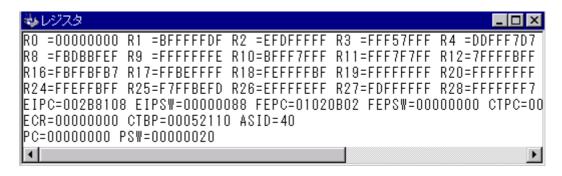

## 表示(V) ~ レジスタ(R)

REGISTER

機能:

レジスタの内容を表示する、レジスタウィンドウを開きます。

#### 操作:

新しくレジスタウィンドウが表示されます。

#### 補足:

● 「第七章 <u>REGISTER</u>」参照。

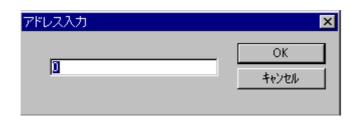

# 表示(V) ~ 逆アセンブル(D)...

UNASM

#### 機能:

メモリの内容を逆アセンブル表示する、逆アセンブラウィンドウを開きます。

#### 操作:

ダイアログ ボックスで、逆アセンブル表示を開始する<u>アドレス(16</u> 進数)を指定し、「OK」ボタン を押してください。

| 🍑 逆アセンブ  | 5:03FF0000 |         | _                      |

|----------|------------|---------|------------------------|

| 03FF000A | 0000       | NOP     | <b>A</b>               |

| 03FF000C | A5FD       | BR      | 0x03FF0000 🗔           |

| 03FF000E | 8454       | SST.H   | R10,0x108[EP]          |

| 03FF0010 | D400       | ZXH     | R20                    |

| 03FF0012 | 7D20       | SLD.HU  | OxFFFFFFFA[EP],R4      |

| 03FF0014 | 5438       | DIVH    | R20,R7                 |

| 03FF0016 | C6E0       | SATADD  | R6,R28                 |

| 03FF0018 | 74267CB0   | SATSUBI | 0xFFFFB07C,R20,R4      |

| 03FF001C | 748D       | SLD.W   | 0x2E8[EP],R17          |

| 03FF001E | AB88       | SATSUB  | R11,R17                |

| 03FF0020 | 41BC       | SLD.H   | 0x82[EP],R23           |

| 03FF0022 | 501A       | ADD     | OxFFFFFFF0,R3 <b>▼</b> |

新しく逆アセンブラウィンドウが表示されます。

#### 補足:

- 逆アセンブラ ウィンドウは複数開くことができます。開くことができるウィンドウ個数は、「<u>表示</u>(<u>V) ~ オプション(O) ~ 表示(V)...</u>」メニューで変更することができます。

- 「第七章 <u>UNASM</u>」参照。

- 「付録 L <u>V850/ME2 内蔵命令 RAM の取り扱い</u>」参照。

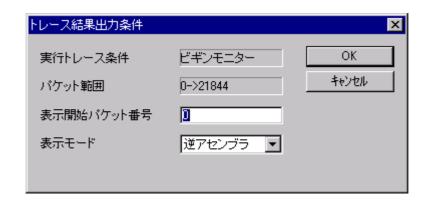

# 表示(V) ~ トレース結果(T)...

HISTORY

#### 機能:

リアルタイムトレース結果の内容を表示する、トレース結果ウィンドウを開きます。

#### 操作:

ダイアログボックスで、<u>表示開始パケット番号</u>、<u>表示モード</u>を指定し、「OK」ボタンを押してください。トレース結果ウィンドウが表示されます。

(逆アセンブラ表示の例)

|     | ≫トレース結果  |         |                                                 |

|-----|----------|---------|-------------------------------------------------|

|     | 03FF001E | NOP     |                                                 |

|     | 03FF0020 | NOP     |                                                 |

|     | 1 0000   | 0003 00 | TRCODE=OA PC=O3FF0022 ASID=O0 JINF=1; BccT(pre) |

|     | 03FF0024 | BR      | 0x03FF0000                                      |

|     | 03FF0000 | NOP     |                                                 |

|     | 03FF0002 | ST.W    | R2,0x0000[R1]                                   |

|     | 03FF0006 | NOP     |                                                 |

|     | 03FF0008 | NOP     |                                                 |

|     | 03FF000A | NOP     |                                                 |

|     | 03FF000C | NOP     |                                                 |

|     | 03FF000E | LD.W    | 0x0000[R1],R2                                   |

|     | 03FF0012 | NOP     |                                                 |

|     | 03FF0014 | NOP     |                                                 |

|     | 03FF0016 | NOP     |                                                 |

|     | 03FF0018 | NOP     |                                                 |

|     | 03FF001A | ADDI    | 0x0001,R2,R2                                    |

| - 1 | 03FF001E | NOP     |                                                 |

|     | 03FF0020 | NOP     |                                                 |

|     | 2 0000   | 0006 00 | TRCODE=OA PC=O3FFO022 ASID=O0 JINF=1; BccT(pre) |

#### 補足:

- 実行トレース条件については、「第八章 設定(S) ~ トレース(T)…」参照。

- 「第七章 HISTORY」参照。

サイクル範囲では、トレース バッファ メモリへ取り込まれたサイクルの範囲を表示します。サイクルの 0 点は「実行トレース条件」により異なります。

ビギン モニター プログラム開始点

エンド モニター プログラム終了点(トレース中止点)

ビギン トリガー/イベント トリガー点 エンド トリガー/イベント トリガー点 ミッド トリガー/イベント トリガー点

インナートリガー/イベント トレース開始 トリガー点

<u>表示開始サイクル</u>では、トレース結果表示ウィンドウの最上行に表示するサイクルを指定します。

表示モードでは、トレース結果表示モードを指定します。次の中から選択します。

パケットトレース出力をパケット単位で表示します。

逆アセンブラ トレース出力をパケット表示と共に命令コードとアセンブラ ニーモニックで表示します。

トレース パケット 表示フォーマット

[トレースパケットフォーマット共通部分]

| DDDDDD | XXXXXXX | CC     | TRCODE=XX | <u> </u>   |

|--------|---------|--------|-----------|------------|

| (Ī)    | (2)     | (3)(4) | (5)       | <b>(6)</b> |

- ① 行番号 6 桁の 10 進整数

- ② タイムスタンプ 8 桁の 16 進数 \*1

- ③ 0または1EXTIN1信号の状態

- ④ 0または1EXTIN2信号の状態

- ⑤ トレース要因コード 2 桁の 16 進数

- ⑥ トレース要因毎に異なる個別表示部分

#### [トレースパケットフォーマット個別部分]

TRCODE=01 OVF=C SSW=C; Start (1)(2) (3)

- 0または1オーバーフローフラグ 1

- (2) 0または1トレースサブスイッチ状態 \*2

- ③ トレーススタートポイント検出

SCF=C TRCODE=02 OVF=C SSW=C; Match Point (1) (2) (3) **(4)**

- 0または1オーバーフローフラグ (1)

- ② 0または1スタートパケット競合フラグ\*3

- ③ 0または1トレースサブスイッチ状態\*2

- マッチポイント検出 4

TRCODE=03: Overflow

1

① トレースデータオーバーフロー発生

JINF=C; TRCODE=08 PC=XXXXXXXX ASID=XX YYYYYY 1 2 3 4

- 分岐先アドレス 8 桁の 16 進数 (1)

- 2 ASID 2 桁の 16 進数

- 3 0または1分岐元パケット付加情報 \*4

- 分岐先 PC トレース要因(割込、例外、分岐命令による分岐(分岐先 PC)、強制スタート)\*5 4

| TRCODE=09        | ①                                                             | ASID=XX<br>②              | JINF=C;           | 4)<br>(4)    | 5<br>5               |          |

|------------------|---------------------------------------------------------------|---------------------------|-------------------|--------------|----------------------|----------|

| ① ② ③ ④ ⑤        | 分岐先/元アト<br>ASID 2 桁の 1<br>0 または 1 分<br>分岐先 PC トレ<br>分岐元 PC トレ | 6 進数<br>岐元パケット<br>⁄ース要因(簀 | 、付加情報<br>割込、例外    | 、分岐命令        | による分岐)*6<br>による分岐、強制 | リスタート)*5 |

| TRCODE=0A        | PC=XXXXXXXX<br>①                                              | ASID=XX                   | JINF=C;           | YYYYY<br>4   | (                    |          |

| ①<br>②<br>③<br>④ | 分岐元アドレス<br>ASID 2 桁の 1<br>0 または 1 分<br>分岐元 PC トレ              | 6 進数<br>岐元パケット            | 付加情報              |              | による分岐(分岐             | 元 PC))*6 |

| TRCODE=0C        | XXXXXXXX X                                                    | XXXXXXX<br>②              | TRG=C;            | Data Wr<br>④ | ite                  |          |

| ①<br>②<br>③<br>④ | アクセスアドレ<br>データ値 2桁<br>0または1トリ<br>データトレース                      | ,4 桁または<br>ガポイント番         | :8 桁の 16<br>§号 *7 |              |                      |          |

| TRCODE=0D        | XXXXXXXX X                                                    | XXXXXXX<br>②              | TRG=C;            | Data Read ④  |                      |          |

| ①<br>②<br>③<br>④ | アクセスアドレ<br>データ値 2桁<br>0または1トリ<br>データトレース                      | ,4 桁または<br>ガポイント番         | :8 桁の 16<br>译号 *7 |              |                      |          |

#### \*1 タイムスタンプ

1MHz で動作するフリーランカウンタの値です。 二つのタイムスタンプの差分を計算することでプログラム実行時間を計測することができます。

#### \*2 トレースサブスイッチ状態

インナートリガまたはインナーイベントモードでトレースを実行すると トレース開始点でトレースが再開されるときに SSW=1 になります。 トレースサブスイッチは MJXDEBW プログラムが制御を行うので、ユーザからは操作できません。

#### \*3 スタートパケット競合フラグ

スタートパケットとマッチポイントパケットが競合した場合、スタートパケットは破棄されマッチポイントパケットには競合を示す SCF=1 が出力されます。

なお Mjxdebw ではスタートポイントとマッチポイントは Mjxdebw プログラムから自動的に設定しますので、ユーザからは操作できません。

#### \*4 分岐元パケット付加情報

V850E は2命令同時実行が可能です。

JINF=1 の場合、実際の分岐元アドレスは表示される(アドレス+2)となります。 なお TRCODE=08 の場合は分岐先アドレスが表示されるので JINF は意味を持ちません。

#### \*5 分岐先 PC トレース要因では以下の文字情報が表示されます。

INT(pst) :割り込み(NMI/INT)

EXCEPT(pst) :例外、トラップ命令(,DBTRP 命令)

RETI (pst) : RETI 命令(,DBRET 命令)

JMP(pst)

: JMP 命令

JR(pst)

: JR 命令

JARL(pst)

: JARL 命令

BccF(pst):条件付分岐命令 Bcond(条件不成立時)BccT(pst):条件付分岐命令 Bcond(条件成立時)

CALLT (pst) : CALLT 命令 SWITCH(pst) : SEITCH 命令 DISPOSE (pst) : DISPOSE 命令 CTRET (pst) : CRET 命令 Force Start : 強制スタート

Unknown : 未定義の分岐要因を示す

#### \*6 分岐元 PC トレース要因では以下の文字情報が表示されます。

INT(pst) :割り込み(NMI/INT)

EXCEPT(pre) : 例外、トラップ命令(,DBTRP 命令)

RETI (pre) : RETI 命令(,DBRET 命令)

JMP(pre)

: JMP 命令

JR(pre)

: JR 命令

JARL(pre)

: JARL 命令

JARL (pre): JARL 命令BccF(pre): 条件付分岐命令 Bcond(条件不成立時)BccT(pre): 条件付分岐命令 Bcond(条件成立時)CALLT 命令: CALLT 命令

CALLT (pre) : CALLT 命令

SWITCH(pre) : SEITCH 命令

DISPOSE (pre) : DISPOSE 命令

CTRET (pre) : CRET 命令

Unknown :未定義の分岐要因を示す

#### \*7 トリガポイント番号

トリガ番号については MJXDEBW プログラムが自動的に0または1を選択します。 ユーザからは操作できません。

# 表示(V) ~ コマンド応答クリア(C)

CLEAR

機能:

コマンド応答フィールドをクリアします。

補足:

● 「第七章 <u>CLEAR</u>」参照。

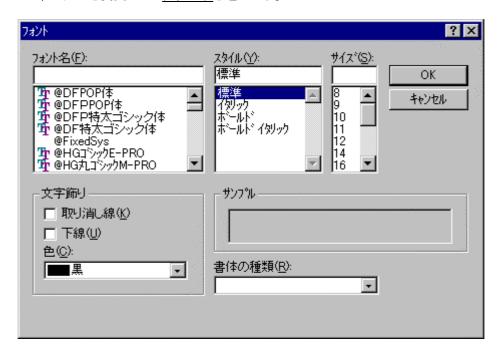

# 表示(V) ~ オプション(O) ~ フォント(F)

#### 機能:

ウィンドウに表示する文字のフォントを変更します。

#### 操作:

コマンド応答(Q)... メモリ表示(M)... レジスタ(R)... 逆アセンブル(D)... トレース結果(T)...

メニューで、フォントを変更したいウィンドウを選びます。

ダイアログ ボックスで、フォント、スタイル、サイズを指定し、「OK」ボタンを押してください。

#### 補足:

\_

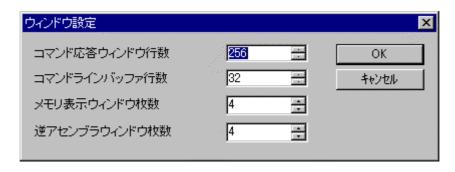

# 表示(V) ~ オプション(O) ~ 表示(V)...

#### 機能:

コマンド ウィンドウ、メモリ ウィンドウ、逆アセンブル ウィンドウの属性を指定します。

#### 操作:

ダイアログ ボックスで、各ウィンドウの属性を指定し、「OK」ボタンを押してください。

#### 補足:

## 変更(M) ~ メモリ(M)...

EXAMINE

#### 機能:

メモリの内容を変更します。

#### 操作:

ダイアログ ボックスで、変更するメモリの<u>アドレス(16</u> 進数)、<u>データ</u>、<u>データ幅、データ型</u>を指定し、「更新」ボタンを押してください。

「更新」ボタンを押すとメモリが変更され、ダイアログの<u>アドレス</u>が自動的に進みます。続けてメモリを変更する場合は、同様の手順を繰り返してください。

メモリの変更が終了したら、「終了」ボタンを押してください。

#### 補足:

- 「第七章 <u>EXAMINE</u>」参照。

- 「付録 L V850/ME2 内蔵命令 RAM の取り扱い」参照。

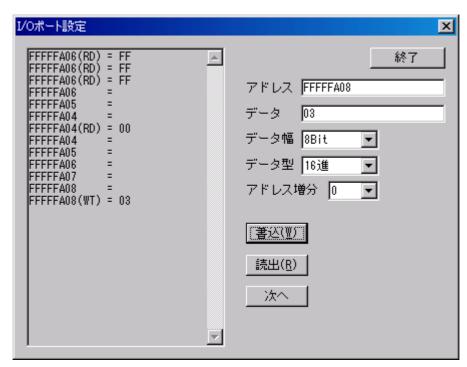

## 変更(M) ~ I/O ポート(P)...

#### 機能:

I/O ポートの内容を変更します。

#### 操作:

ダイアログ ボックスで、変更する I/O ポートの<u>アドレス(16</u> 進数)、<u>データ、データ幅</u>、<u>データ型</u> <u>アドレス増分</u>を指定し、「書込」または「読出」ボタンを押してください。

「次へ」ボタンを押すとI/Oポートアクセスを行わずにアドレスの増減ができます。

#### 補足:

● MJX440 for NB85E ではメモリマップド I/O に対してアクセスを行います。

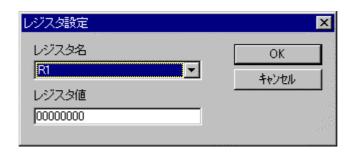

## 変更(M) ~ レジスタ(R)...

REGISTER

機能:

レジスタの内容を変更します。

操作:

ダイアログ ボックスで、レジスタ名、レジスタ値を指定し、「OK」ボタンを押してください。

#### 補足:

● 「第七章 <u>REGISTER</u>」参照。

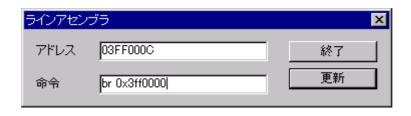

## 変更(M) ~ アセンブラ(A)...

#### 機能:

メモリの内容をアセンブラで変更します。

#### 操作:

ダイアログ ボックスで、変更するメモリの<u>アドレス(16</u> 進数)、アセンブラの<u>命令</u>を指定し、「更新」ボタンを押してください。

「更新」ボタンを押すとメモリが変更され、ダイアログの<u>アドレス</u>が自動的に進みます。続けてメモリを変更する場合は、同様の手順を繰り返してください。

メモリの変更が終了したら、「終了」ボタンを押してください。

#### 補足:

- シンボルは入力できません。

- 16 進数は、0x1234 のように先頭に「0x」を付加してください。

- 「付録 L V850/ME2 内蔵命令 RAM の取り扱い」参照。

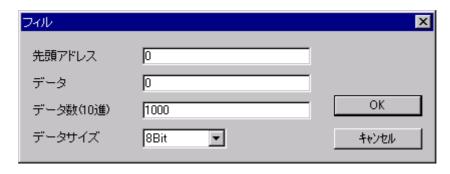

# 変更(M) ~ フィル(F)...

FILL

#### 機能:

メモリの内容をフィルします。

#### 操作:

ダイアログ ボックスで、変更するメモリの<u>先頭アドレス(16</u> 進数)、<u>データ(16</u> 進数)、<u>データ数</u> (10 進数)、<u>データ サイズ</u>を指定し、「OK」ボタンを押してください。

#### 補足:

- 「第七章 FILL」参照。

- 「付録 L V850/ME2 内蔵命令 RAM の取り扱い」参照。

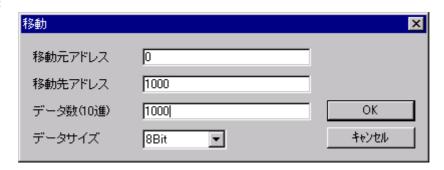

## 変更(M) ~ 移動(M)...

MOVE

機能:

メモリの内容をブロック転送します。

#### 操作:

ダイアログ ボックスで、変更するメモリの<u>移動元アドレス(16</u> 進数)、<u>移動先アドレス(16</u> 進数)、 <u>データ数(10</u> 進数)、<u>データ サイズ</u>を指定し、「OK」ボタンを押してください。

#### 補足:

● 「第七章 <u>MOVE</u>」参照。

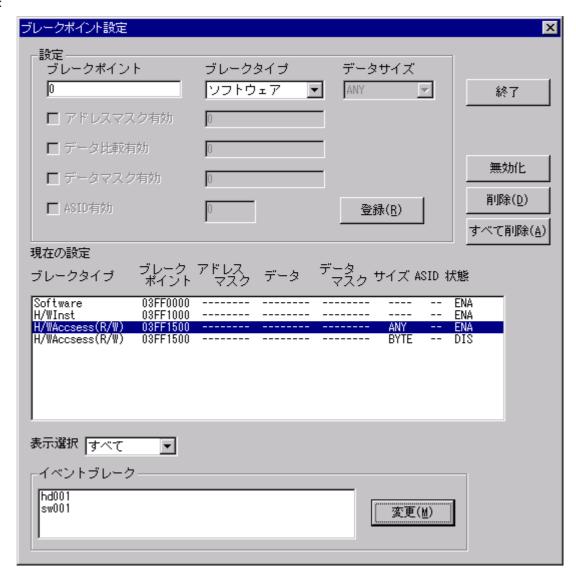

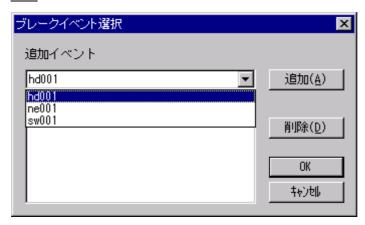

# 設定(S) ~ ブレークポイント(B)...

ΒP

機能:

ブレークポイントを設定します

#### 操作:

設定フレームにある<u>ブレークタイプを</u>選択し、<u>ブレークポイント(16</u> 進数)を設定します。「登録」 ボタンを押すと、ブレークポイントを設定できます。

設定されたブレークポイントは、「現在の設定」に表示されます。

表示選択を選択すると、現在の設定の表示が変更されます。

現在の設定の中からひとつのブレークポイントを選択し「無効化」ボタンを押すと、ブレークポイントを無効化できます。同様の手順で「有効化」と「削除」ができます。

「すべて削除」ボタンを押すと、ブレークポイントをすべて削除します。

設定フレームにある<u>イベントブレーク</u>の「変更」ボタンを押すと、以下のような<u>ブレークイベント</u> 選択画面が表示されます。

追加イベントからイベント名を選択して、「追加」一「OK」ボタンを押してください。

ブレークポイントの設定が終了したら、「終了」ボタンを押してください。

#### 補足:

- 設定フレーム内の登録は、<u>ブレークタイプを</u>選択すると、それ以下の項目は設定必要な場合のみ 入力できるようになっています。

- 「第七章 <u>BP</u>」参照。

- トレーストリガとして再利用したブレークポイントは削除できません。トレーストリガを無効にしてから削除してください。

# 設定(S) ~ トレース(T)...

TRACE

#### 機能:

リアルタイム トレースのトレース モードを表示/設定します。

#### 操作:

(1)命令トレース条件の設定

ダイアログボックスの命令タブで、トレースモードを設定し、「OK」ボタンを押してください。 トレースモードの設定は次のとおりです。

命令トレース有効

チェックするとトレース全体が有効になります。

トレースモード トレースモードは命令トレースのモードを指定します。トレースモードは以下 から選択します。

完全モード

通常モード

トレース条件

トレース条件を選択します。トレース条件は、以下の中から選択します。

ビギン モニター

エンド モニター

ビギントリガー

エンドトリガー

ミッドトリガー

インナートリガ

ビギン イベント

エンド イベント

ミッド イベント

インナーイベント

レングス

トレースバッファの長さを指定します。長さの単位はトレースワードです。「トリガーモード」がビギンモニター/ミッドトリガー/インナートリガ/ミッドイベント/インナーイベントのとき設定できます。「レングス」に設定できる値は 1 ~131071 です。

トリガーアドレス

トリガー アドレス情報を設定します。「トレース モード」がビギン トリガー/ミッド トリガー/エンド トリガー/インナートリガの場合指定できます。

中断アドレス

中断アドレス情報を設定します。「トレース モード」がインナートリガの場合 設定できます。

ASID

チェックを有効にすると ASID 条件が有効になります。

トレース要因

チェックを有効にすると、トレース要因を設定できます。

トリガーイベントと設定します。

開始イベントインナーイベント条件のトレース開始イベントを指定します。

終了イベント インナーイベント条件のトレース中断イベントを指定します。

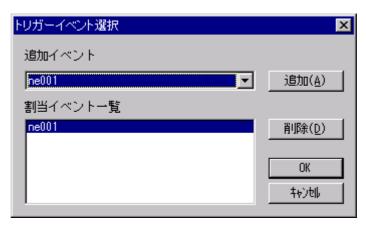

イベント設定ウィンドウ トリガーイベント、開始イベント、終了イベントの「変更」ボタンを押すと、下 のようなイベント設定ウィンドウが表示されます。「追加イベント」からイベント

を選択して「追加」ボタンを押します。イベントの設定を解除したい場合は、 「割当イベント一覧」から削除するイベントを選択して、「削除」ボタンを押し

ます。

<トリガーイベントのイベント設定ウィンドウ>

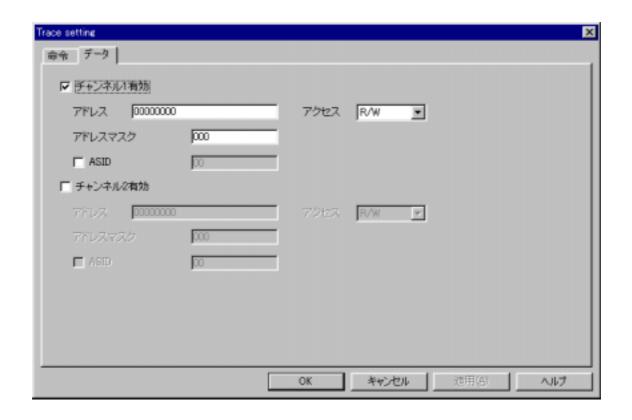

#### (2)データトレース条件の設定

ダイアログボックスのデータタブで、チャンネル有効を設定し、「OK」ボタンを押してください。

#### チャンネルの設定は次のとおりです

チャンネル有効

有効にしたいチャンネル番号のチェックボックスを選択します。

選択したチャンネルの<u>アドレス(16</u> 進数)を指定し<u>アクセス</u>データを選択します。必要に応じて<u>アドレスマスク(16</u> 進数)、<u>ASID 条件</u>の有効/無効を決定します。

#### 補足:

● 「第七章 <u>TRACE</u>」参照。

## 設定(S) ~ イベント(E)...

**EVENT**

機能:

イベント機能構成と設定されている全イベントを表示します。

操作: ダイアログボックスの「新規イベント」フレームを設定し、「登録」ボタンを押してください。

作成したイベントの詳細が表示されます。

「新規イベント」の詳細設定は、次のとおりです。

イベント名

イベント識別名を指定します。イベント識別名は、カンマ、スペー

ス、タブを除く印字可能半角文字を指定します。

タイプ

イベントの内容を選択します。

アドレス範囲 イベント開始アドレス(16進数)を設定します。

ASID 有効 ASID 条件の有効/無効を決定します。

シーケンス器を使用する場合は、「SEQ 器設定」フレームの <u>SEQ 器段数</u>と パスカウントを設定してください。

シーケンス器スイッチイベントを割り当てる場合は、イベント一覧ウィンドウから対象となるイベントの詳細を選択し、コンボボックスから、<u>シーケンス器スイッチイベント</u>を選択して「割当」ボタンを押してください。

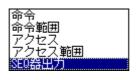

(シーケンス器スイッチイベント)

「開放」ボタンを押すと、選択されている<u>シーケンス器スイッチイベント</u>が開放されます。「削除」 ボタンを押すと、選択されたイベントが削除されます。

同様にして外部トリガー出力イベントの割り当てを行うことができます。

チャンネル割当が行われているイベントは\*マークで表示が行われます。 割当対象の略称は以下のとおりです。

BP :ブレークポイント

TT : トレース トリガ ポイント

TS :トレース 開始ポイント

TE : トレース 終了ポイント

OT:外部トリガ出力ポイント

S1 :SEQ 器スイッチ1

S2 :SEQ 器スイッチ 2 S3 :SEQ 器スイッチ 3

S4 :SEQ 器スイッチ 4

SC :SEQ 器クリアポイント

終了する場合は、「終了」ボタンを押してください。

#### 補足:

● 「第七章 <u>EVENT</u>」参照。

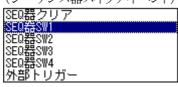

# 設定(S) ~ 設定の読出(L)...

SETLOAD

#### 機能:

ブレークポイント、イベントおよびトレースの設定を、ファイルから読み込みます。

#### 操作:

ダイアログボックスで、ファイル名を指定し、「開く」ボタンを押してください。

#### 補足:

● 「<u>設定(S) ~ 設定の保存(S)…</u>」メニューで作成されたファイルを指定してください。

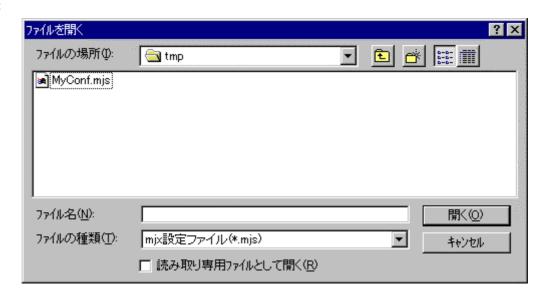

# 設定(S) ~ 設定の保存(S)...

SETSAVE

#### 機能:

ブレークポイント、イベントおよびトレースの設定をファイルへ保存します。

#### 操作:

ダイアログ ボックスで、ファイル名を指定し、「開く」ボタンを押してください。

#### 補足:

● 保存したファイルは「<u>設定(S) ~ 設定の読出(L)...</u>」メニューで指定することができます。

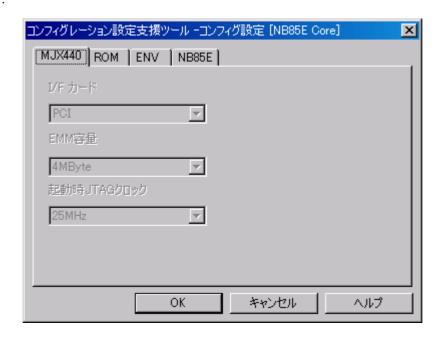

# 設定(S) ~ コンフィグレーション(C) ~ 設定(S)...

CONFIG

#### 機能:

MJXDEBW の環境を設定します。

#### 操作:

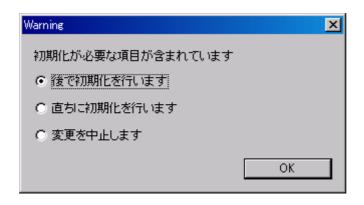

コンフィグレーション設定支援ツールが起動します。

変更する項目を設定してください。

初期化が必要な項目が変更された場合、確認ダイアログが表示されます。 適切な処置を選択し「OK」ボタンを押してください。

#### 補足:

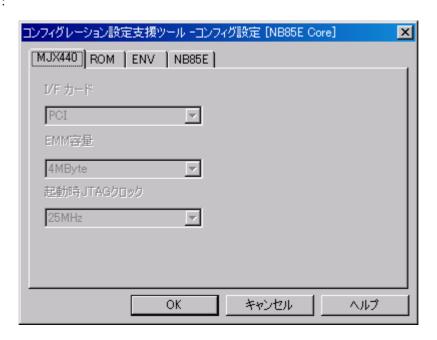

- MJXDEBW 起動中に変更できない項目は反転表示されます。

- 「第七章 <u>CONFIG</u>」参照。

# 設定(S) ~ コンフィグレーション(C) ~ 表示(V)...

CONFIG

#### 機能:

MJXDEBW の環境を表示します。

#### 操作:

#### 補足:

● 「第七章 CONFIG」参照。

# 設定(S) ~ コンフィグレーション ~ 上書き保存(E)

CONFIG

#### 機能:

現在のコンフィグレーションの設定を MJXDEBW 起動時に指定したコンフィグレーションファイルへ上書き保存します。

操作:

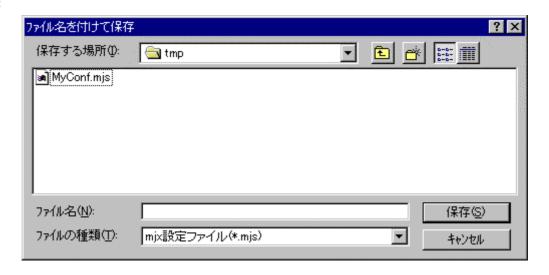

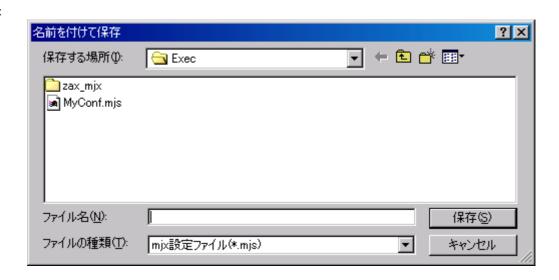

# 設定(S) ~ コンフィグレーション ~ 名前を付けて保存(A)

CONFIG

#### 機能:

現在のコンフィグレーションの設定を新たなコンフィグレーションファイルへ保存します。

#### 操作:

ダイアログボックスでファイル名を指定し、「保存」ボタンを押してください。

# ヘルプ(H) ~ トピックの検索(H)

#### 機能:

MJX440 for NB85E に関するマニュアル画面が表示されます。

#### 操作:

マニュアル画面は「しおり」またはしおりの最後に記述されている「検索項目」のシートから参照してください。

# ヘルプ(H) ~ MJXDEBW のバージョン情報(A)

VERSION

機能:

バージョンを表示します

操作:

#### 補足:

● 「第七章 <u>VERSION</u>」参照。

## 第九章 高速ダウンロード

高速ダウンロードを行なうための手順について記述しています。

MJX バイナリ ファイルを作成することによって、プログラムを高速でダウンロードすることができます。 およそのダウンロード速度は、次のとおりです。(PCI カード使用の時)

- N-Wire ケーブル接続時、480K バイト/秒\*1(JTAG クロック 25MHz)

- ROM インサーキット接続時、4M バイト/秒

MJX バイナリファイルは、ファイル変換プログラム MJXCVT を使用して作成します。MJXCVT は、S レコードファイルを MJX バイナリファイルへ変換するプログラムです。使用方法は、次のとおりです。 MS-DOS プロンプト内から実行してください。

#### MJXCVT の使用方法

mjxcvt [-o offset] infile [outfile]

-o offset 出力ファイルにオフセット アドレスを加算する infile入力ファイル名 outfile 出力ファイル名 (省略時は、infile の拡張子を.mjx にしたファイル名)

## MJX バイナリ ファイルのダウンロード

MJXCVT で作成された $\underline{MJX}$  バイナリ ファイルは、 $\underline{MJX440}$  コマンドの LOAD コマンドでダウンロードすることができます。

load myfile.mjx

## 付録 A 仕様

本体寸法 31mm(高さ) x 149mm(幅) x 186mm(奥行き)

本体重量 450g

電源 (AC アダプタ) 入力 AC100~240V 50Hz/60Hz

出力 DC 5V±5% 3.0A

ROM プローブ ケーブル 300mm 外部トリガ ケーブル 300mm 使用温度範囲 0℃~35℃ 保存温度範囲 -10℃~55℃ 周囲湿度範囲 30%~85%

対応 ROM 「付録 D ROM プローブ」参照

対応 ROM 個数 8 ビット 1 個、 2 個、 4 個 16 ビット 1 個、 2 個

エミュレーション メモリ容量 4M バイト(標準) アクセス タイム CS から 50n 秒

インターフェース パラレル (PCI、PCMCIA カード)

ターゲット インターフェース N-Wire コネクタ

ROM ソケット

対応 CPU NB85E Core

ダウンロード速度 480K バイト/秒\*1 (N-Wire 接続、JTAG クロック25MHzの場合)

4M バイト/秒 (ROM インサーキット接続時)

対応デバッガ Green Hills MULTI (対応 OS は Windows98/NT4.0/2000/XP)

ブレークポイント機能 ハードウエア × 2

ソフトウェア × 128

イベントブレーク 命令 最大 8

アクセス 最大 4

トレース機能 トレース メモリ 48bit × 128K

トレース クロック 66MHz max (CPU に依存)

トレース条件 10 種 タイムスタンプ 32bit

制限事項 「付録 B ターゲット システムの制限事項」参照

<sup>\*1</sup> ダウンロードの速さは JTAG クロックを高く設定する程、高速になります。

## 付録 B ターゲット システムの制限事項

MJX440を使用するためには、ターゲットシステムが次の条件を満足している必要があります。

● N-Wire 仕様のコネクタを実装している。

さらに、ROMインサーキット接続するためには、次の条件を満足している必要があります。

- ROM ソケットが実装されている。

- ROM がバンク化されていない。

- ROM が複数個実行されている場合、すべての ROM のアドレス信号が同じか、ROM のアドレスが 連続している。

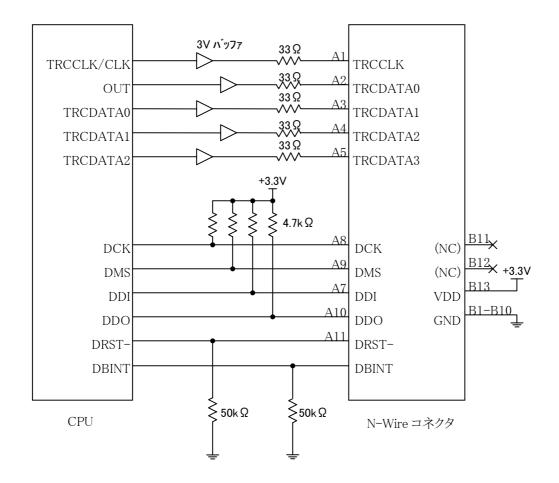

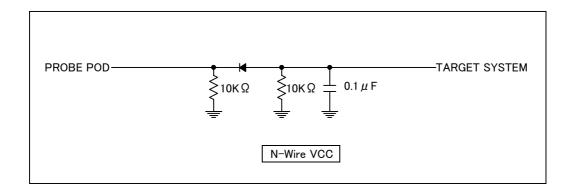

## 付録 C N-Wireコネクタ

### ピンアサイン

| TRCCLK   | A01 | B01 | GND |

|----------|-----|-----|-----|

| TRCDATA0 | A02 | B02 | GND |

| TRCDATA1 | A03 | B03 | GND |

| TRCDATA2 | A04 | B04 | GND |

| TRCDATA3 | A05 | B05 | GND |

| TRCEND   | A06 | B06 | GND |

| DDI      | A07 | B07 | GND |

| DCK      | A08 | B08 | GND |

| DMS      | A09 | B09 | GND |

| DDO      | A10 | B10 | GND |

| DRST-    | A11 | B11 | NC  |

| PORT0    | A12 | B12 | NC  |

| PORT1    | A13 | B13 | VDD |

#### 推奨コネクタ

- KEL 社製 8830E-026-170S (ストレート)

- KEL 社製 8830E-026-170L (ライトアングル)

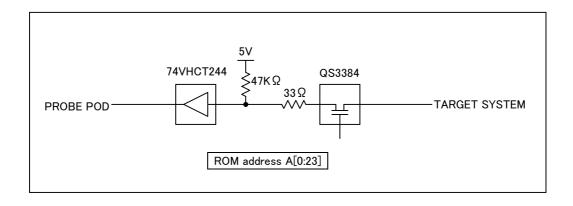

#### ターゲット システムの推奨回路

#### 注意事項

- CPU~N-Wire コネクタ間のパターンは、できるだけ短くしてください。(100mm 以下)

- TRCCLK/CLKOUT~TRCCLK 間とDCK~DCK 間のパターンは、GND でシールドしてください。

- MJX440 は、B13 VDD をターゲットプロービングバッファの電源に使用しています。

#### 3V バッファ推奨品

- TI 社製 SN74LVC541A

- 東芝社製 TC74LCX541F

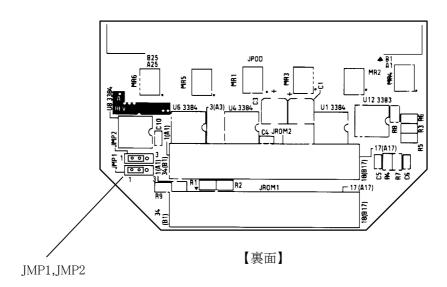

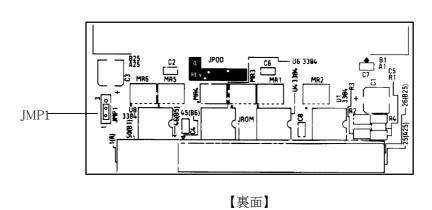

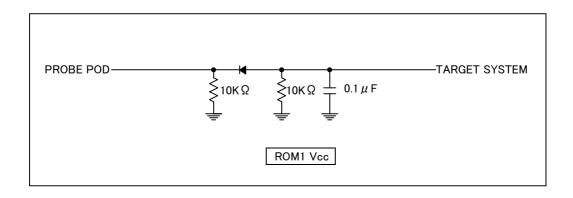

# 付録 D ROM プローブ

J-101A (32pin-8bit ROM 用)

J-102A (40/42pin-16bit ROM 用 - バスサイシング 16bit 固定)

## J-103A (40/42pin-16bit ROM 用 - バスサイジング機能無し)

【裏面】

## J-104A (40/42pin-16bit ROM 用 - バスサイジング8bit 固定)

【裏面】

## J104(40/42pin-16bit ROM 用)

【裏面】

## ROM プローブ基板 J-101A ジャンパ設定:

| ROM プラグ  | ジャンパ設定        | ROM 容量         | 対応 ROM         | ROM メーカ    |

|----------|---------------|----------------|----------------|------------|

| 32pin    | JMP1 1-2 ショート | 128K x 8bit    | HN27C101AG     | Hitachi    |

|          | JMP2 2-3 ショート | (0x20000byte)  | μ PD27C1001AD  | NEC        |

| (27010)  |               |                | TC571000D      | Toshiba    |

|          |               |                | TC571000AD     | Toshiba    |

|          |               |                | TC57H1000AD    | Toshiba    |

|          |               |                | M5M27C101K     | Mitsubishi |

|          |               |                | MBM27C1001-nnZ | Fujitsu    |

|          |               |                | 27010          | intel      |

|          |               |                | 27C010         | intel      |

|          |               |                | Am27C010       | AMD        |

| 32pin    | JMP1 1-2 ショート | 256K x 8bit    | μ PD27C2001D   | NEC        |

| (27020)  | JMP2 1-2 ショート | (0x40000byte)  | M5M27C201K     | Mitsubishi |

|          |               |                | Am27C020       | AMD        |

| 32pin    | JMP1 1-2 ショート | 512K x 8bit    | HN27C4001G     | Hitachi    |

| (27040)  | JMP2 1-2 ショート | (0x80000byte)  | μ PD27C4001DZ  | NEC        |

|          |               |                | TC574000D      | Toshiba    |

|          |               |                | TC574000DI     | Toshiba    |

|          |               |                | M5M27C401K     | Mitsubishi |

|          |               |                | MBM27C4001-nnZ | Fujitsu    |

|          |               |                | 27040          | intel      |

|          |               |                | Am27C040       | AMD        |

| 32pin    | JMP1 1-2 ショート | 1024K x 8bit   | Am27C080       | AMD        |

| (27080)  | JMP2 1-2 ショート | (0x100000byte) |                |            |

| 32pin    | JMP1 2-3 ショート | 128K x 8bit    | HN27C301AG     | Hitachi    |

| (271000) | JMP2 2-3 ショート |                | μ PD27C1000AD  | NEC        |

|          |               |                | TC571001D      | Toshiba    |

|          |               |                | TC571001AD     | Toshiba    |

|          |               |                | TC57H1001AD    | Toshiba    |

|          |               |                | M5M27C100K     | Mitsubishi |

|          |               |                | MBM27C1000-nnZ | Fujitsu    |

## ROM プローブ基板 J-102A ジャンパ設定

| ROM プラグ          | ジャンパ設定        | ROM 容量         | 対応 ROM      | ROM メーカ |

|------------------|---------------|----------------|-------------|---------|

| 40pin            | JMP1 1-2 ショート | 256K x 16bit   | HN27C4000G  | Hitachi |

| (27C4000 16bit)  |               | (0x80000byte)  | Am27C400    | AMD     |

| 42pin            | JMP1 2-3 ショート | 512K x 16bit   | μ PD27C8000 | NEC     |

| (27C8000 16bit)  |               | (0x100000byte) | Am27C800    | AMD     |

| 42pin            | JMP1 1-2 ショート | 1024K x 16bit  |             |         |

| (27C16000 16bit) |               | (0x200000byte) |             |         |

## ROM プローブ基板 J-103A ジャンパ設定

| ROM プラグ  | ジャンパ設定        | ROM 容量        | 対応 ROM         | ROM メーカ |

|----------|---------------|---------------|----------------|---------|

| 40pin    | JMP1 2-3 ショート | 64K x 16bit   | HN27C1024HG    | Hitachi |

| (271024) |               | (0x20000byte) | μ PD27C1024D   | NEC     |

|          |               |               | μ PD27C1024AD  | NEC     |

|          |               |               | TC57H1024D     | Toshiba |

|          |               |               | TC57H1024AD    | Toshiba |

|          |               |               | MBM27C1024-nnZ | Fujitsu |

|          |               |               | 27210          | intel   |

|          |               |               | 27C210         | intel   |

|          |               |               | Am27C1024      | AMD     |

| 40pin    | JMP1 1-2 ショート | 128K x 16bit  | Am27C2048      | AMD     |

| (272048) |               | (0x40000byte) |                |         |

| 40pin    | JMP1 1-2 ショート | 256K x 16bit  | HN27C4096G     | Hitachi |

| (274096) |               | (0x80000byte) | HN27C4096HG    | Hitachi |

|          |               |               | HN27C4096AG    | Hitachi |

|          |               |               | HN27C4096AHG   | Hitachi |

|          |               |               | TC574096D      | Toshiba |

|          |               |               | MBM27C4096-nnZ | Fujitsu |

|          |               |               | 27240          | intel   |

|          |               |               | Am27C4096      | AMD     |

### 付録 D ROM プローブ

## ROM プローブ基板 J-104A ジャンパ設定

| ROM プラグ         | ジャンパ設定        | ROM 容量         | 対応 ROM      | ROM メーカ |

|-----------------|---------------|----------------|-------------|---------|

| 40pin           | JMP1 1-2 ショート | 512K x 8bit    | HN27C4000G  | Hitachi |

| (27C4000 8bit)  |               | (0x80000byte)  | Am27C400    | AMD     |

| 42pin           | JMP1 2-3 ショート | 1024K x 8bit   | μ PD27C8000 | NEC     |

| (27C8000 8bit)  |               | (0x100000byte) | Am27C800    | AMD     |

| 42pin           | JMP1 1-2 ショート | 2048K x 8bit   |             |         |

| (27C16000 8bit) |               | (0x200000byte) |             |         |

# 付録 E 対応 ROMピンアサイン

| Unn       | 1     | 32       | Vcc  | Vnn  | 1     |       | 32   | Vcc    |

|-----------|-------|----------|------|------|-------|-------|------|--------|

| Vpp       | 1     | 32       |      | Vpp  | 1     |       |      |        |

| A16       | 2     | 31       | PGM* | A16  | 2     |       | 31   | PGM*   |

| A15       | 3     | 30       | NC   | A15  | 3     |       | 30   | A17    |

| A12       | 4     | 29       | A14  | A12  | 4     |       | 29   | A14    |

| A7        | 5     | 28       | A13  | A7   | 5     |       | 28   | A13    |

| A6        | 6     | 27       | A8   | A6   | 6     |       | 27   | A8     |

| A5        | 7     | 26       | A9   | A5   | 7     |       | 26   | A9     |

| <b>A4</b> | 8     | 25       | A11  | A4   | 8     |       | 25   | A11    |

| A3        | 9     | 24       | OE*  | A3   | 9     |       | 24   | $OE^*$ |

| A2        | 10    | 23       | A10  | A2   | 10    |       | 23   | A10    |

| A1        | 11    | 22       | CE*  | A1   | 11    |       | 22   | $CE^*$ |

| A0        | 12    | 21       | I/O7 | A0   | 12    |       | 21   | I/O7   |

| I/O0      | 13    | 20       | I/O6 | I/O0 | 13    |       | 20   | I/O6   |

| I/O1      | 14    | 19       | I/O5 | I/O1 | 14    |       | 19   | I/O5   |

| I/O2      | 15    | 18       | I/O4 | I/O2 | 15    |       | 18   | I/O4   |

| Vss       | 16    | 17       | I/O3 | Vss  | 16    |       | 17   | I/O3   |

|           | J-101 | IA 27010 |      |      | J-101 | IA 27 | 7020 |        |

| Vpp  | 1           | 32 | Vcc  | A19  | 1     |          | 32 | Vcc    |

|------|-------------|----|------|------|-------|----------|----|--------|

| A16  | 2           | 31 | A18  | A16  | 2     | <u>-</u> | 31 | A18    |

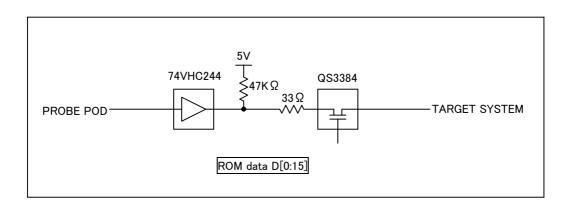

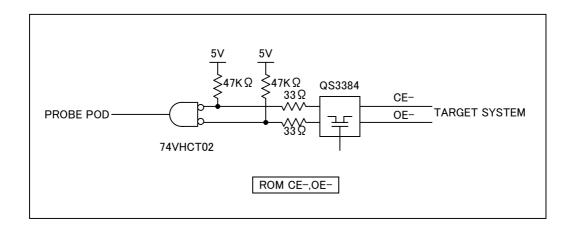

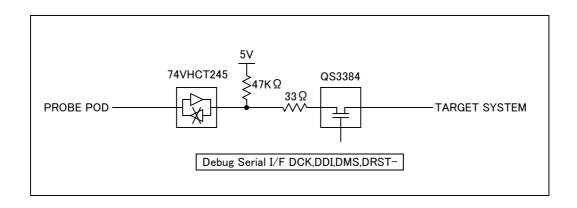

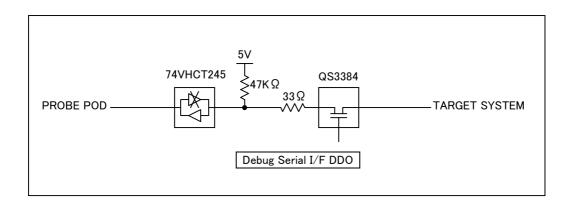

| A15  | 3           | 30 | A17  | A15  | 3     |          | 30 | A17    |